Приборы и техника эксперимента, 2022, № 6, стр. 5-18

СОВРЕМЕННЫЕ СПЕЦИАЛИЗИРОВАННЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ ДЛЯ ПЛОСКИХ РЕЗИСТИВНЫХ СЧЕТЧИКОВ (обзор)

a Институт ядерных исследований РАН

117312 Москва, просп. 60-летия Октября, 7а, Россия

* E-mail: Eugueni.oussenko@cern.ch

Поступила в редакцию 30.03.2022

После доработки 20.05.2022

Принята к публикации 21.05.2022

- EDN: HIZPBG

- DOI: 10.31857/S0032816222050305

Аннотация

Рассмотрены специализированные интегральные схемы усилителей-дискриминаторов DIE8 (ATLAS, CERN), NINO (ALICE, CERN) и PADI (CBM, GSI), разработанных специально для применений с новым типом многоканальных детекторов − плоскими резистивными камерами (RPC − Resistive Plate Chamber). Показаны основные тенденции развития, сформированные в период создания новых больших экспериментов на Большом адронном коллайдере (LHC). Сравниваются основные характеристики интегральных схем, мотивировка постановки задачи на проектирование, проблемы и особенности применения.

ВВЕДЕНИЕ

Построение современных детекторов частиц давно встало на путь использования специализированных интегральных схем (СИМС). Причин тому много – это повышение качества и надежности систем считывания, снижение их стоимости, энергопотребления и габаритов. Со временем приоритеты менялись − от простейших решений в сторону развитой функциональности, например, с возможностью совмещения аналоговых и цифровых частей схем.

Первые СИМС 60-х годов повторяли принципы построения и схемотехнику прототипов электроники считывания, построенной на дискретных элементах, и представляли собой различные типы многоканальных зарядочувствительных [1], трансимпедансных или масштабных усилителей, предназначенных для координатных детекторов. Позже получили развитие СИМС многоканальных усилителей-дискриминаторов [2–4]. Долгое время совмещение аналоговых и цифровых частей электроники было проблемой вследствие помех и шумов, порождаемых при переключении последних. Это, главным образом, относится к схемам ТТЛ-логики. Технология ЭСЛ применялась ограниченно из-за высокого энергопотребления. Со временем развитие схем, выполненных по технологии CMOS (complementary metal-oxide-semiconductor), создало предпосылки для решения этой проблемы.

CMOS-технология за счет резкого снижения энергопотребления единичными элементами схемы привела к существенному прогрессу в построении больших интегральных схем коммерческих применений и, в свою очередь, в технологии создания СИМС для физики частиц. Особенностью работы логического элемента CMOS является весьма незначительное потребление тока в статическом режиме и малые помехи в моменты переключения, что привело со временем к возможности совмещения на одном кристалле CMOS-чипа аналоговых и цифровых частей схем.

Первые CMOS-схемы 60−70-х годов прошлого столетия имели низкое быстродействие, но в соответствии с законом Мура довольно быстро значительно выросли быстродействие и степень интеграции. К 90-м годам прогресс в разработке CMOS-схем привел к появлению быстродействующих коммерческих интегральных схем, после чего последовали многочисленные попытки создания многофункциональных СИМС для физики частиц. Далеко не все из них известны и получили путевку в эксперимент, но опыт их разработки и путь преодоления ошибок дал жизнь тем, что будут описаны ниже.

СПЕЦИАЛИЗИРОВАННЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ УСИЛИТЕЛЕЙ-ДИСКРИМИНАТОРОВ ДЛЯ ВРЕМЯПРОЛЕТНЫХ ДЕТЕКТОРОВ

В современных экспериментах по физике все большую роль играют многоканальные детекторы, предназначенные для точного определения времени пролета частиц. Быстрая времяпролетная электроника считывания, построенная на дискретных компонентах и обладающая полосой частот более 500 МГц, характеризуется высокими мощностью потребления, 1−2 Вт/канал, и стоимостью, 15−25 $/канал.

При создании новых экспериментов на Большом адронном коллайдере с проектируемым числом каналов в десятки и сотни тысяч появилась необходимость в разработке первой специализированной интегральной схемы для времяпролетных камер RPC (Resistive plate chamber).

Началу разработки чипа предшествовали работы по тестированию камер, использующих различные типы считывающей электроники и построенных на дискретных элементах. Успешность разработки нового чипа существенно зависит от качества исследований прототипов в совокупности с изучением свойств камер RPC. Результаты исследований являются основой постановки задачи на проектирование нового чипа. Особенностью макетирования прототипов является вычленение свойств электронного канала считывания из результатов исследований камер для аргументированной постановки задачи на проектирование СИМС.

СПЕЦИАЛИЗИРОВАННАЯ ИНТЕГРАЛЬНАЯ СХЕМА ДЛЯ КАМЕР RPC ЭКСПЕРИМЕНТА ATLAS

Одной из первых интересных разработок на полевых транзисторах (еще не CMOS) была специализированная интегральная схема на основе технологии GaAs MESFET 0,6 um фирмы Gigabit Logic, специализирующейся на производстве высокоскоростных интегральных схем на основе арсенида галия [2]. Для разработки интегральной схемы использовалось SPICE QEDA моделирование на основе элементов Triquint GaAs FET библиотеки. В качестве базового элемента был выбран DFET полевой транзистор с высокими рабочими характеристиками, который используется в основном для сложных микроволновых приложений в качестве малошумящего усилителя сигнала. На рис. 1 показана упрощенная схема канала регистрации и 8-канальная структура специализирванной интегральной схемы. Работы по созданию чипа начались в начале 90-х годов, когда еще не было прецедентов проектирования быстродействующих чипов по кремниевой CMOS-технологии, и технология на основе арсенида галия преобладала по быстродействию. Чип разрабатывался для применений в камерах RPC мюонного триггера эксперимента ATLAS, зарядовый спектр которых простирается до минимальных значений порога срабатывания, 100−150 мкВ, что потребовало обеспечения высокого коэффициента усиления, 1500, в широкой полосе частот. Технология с GBWP (Gain Band Width Product) ~100 ГГц представлялась для этого идеальной.

8-канальная СИМС разваривалась непосредственно на печатную плату и не имела ни корпуса, ни собственного наименования, но во внутренней документации эксперимента ATLAS упоминалась как DIE8. Чип представляет собой простейший усилитель-дискриминатор (см. рис. 1) с однофазным высокоомным входом (около 2 кОм). Усилитель сигнала с общим коэффициентом усиления 1500 состоит из трех каскадов простейшей схемотехники без цепей стабилизации режимов каскадов усиления, с межкаскадными RC-связями, однофазным выходным драйвером в стандарте ECL и установкой общего порога на все каналы. Схемотехника строится на основе типовых решений, характерных для усилителей СВЧ-диапазона фирмы Gigabit Logic. Характеристики чипа DIE8 описаны скудно [2]. Указанное время нарастания обоих фронтов 1.5 нс и полоса частот предусилителя 100 МГц при заявленном коэффициенте усиления 1500 соответствует технологии GBWP ~100 ГГц. Расчетный уровень собственных шумов схемы составил 8000e.

Опыт использования интегральной схемы DIE8 показал несколько просчетов при ее проектировании.

Главная ошибка в постановке задачи по разработке DIE8 состояла в неинвертирующем характере общего усиления, что привело к положительной связи входа и выхода канала и общей неустойчивости многоканальной СИМС.

Еще одной проблемой стал высокоомный входной каскад, не позволивший реализовать минимальную величину порога 100 мкВ, что потребовало введения дополнительного внешнего каскада на биполярном транзисторе для преобразования импеданса стрипа 25 Ом во входное сопротивление чипа 1 кОм.

Выходной каскад DIE8 с однофазным выходом создает значительные помехи при работе с низкими порогами и не предназначен для передачи коротких импульсов. В результате выход каждого канала вынужденно был дополнен внешним дифференциальным драйвером для работы на симметричную линию. Только эти дополнительные каскады позволили обеспечить требуемые параметры считывающей электроники камер RPC мюонного триггера эксперимента ATLAS. При этом требования технического задания не были удовлетворены: по полосе частот − примерно 70 МГц вместо 100−150 МГц, по величине минимального порога − до 200 мкВ и по энергопотреблению − увеличение с 25 до 95 мВт. Такова оказалась плата за ошибки в постановке задачи для системы считывания с количеством каналов около 360 тысяч.

Сводной таблицы электрических параметров DIE8 не публиковалось, и в тексте публикации нет объяснения, как измерены указанные характеристики [2].

ПЕРВАЯ СИМС ДЛЯ ВРЕМЯПРОЛЕТНЫХ ПРИМЕНЕНИЙ − NINO-ЧИП

Первым возможным прототипом нового чипа стал, разумеется, СИМС DIE8. Однако обсуждения результатов его применения привели к необходимости полного пересмотра концепции проектирования и отказа от передачи проекта сторонней фирме, специалисты которой не владеют сложной спецификой, сложившейся в экспериментальной физике. Кроме того, опыт создания СИМС показал необходимость итерационного процесса при доведении чипа до требуемых кондиций, что входит в противоречие с договорными отношениями со сторонней организацией. На рис. 2 представлены фотографии NINO СИМС: слева − без корпуса, разваренная на печатную плату, в центре − в корпусе TAPP76.

Рис. 2.

Слева − NINO-чип, разваренный на печатную плату; в центре − NINO-чип в корпусе TAPP76; справа − зависимость шумового заряда от емкости детектора.

Разработка специализированного чипа NINO [3] для времяпролетной системы эксперимента ALICE проводилась в соответствии с базовыми параметрами, представленными в табл. 1. В основу разработки интегральной схемы легли результаты исследований нескольких прототипов канала считывания, выполненных в коллаборации ALICE TOF. По результатам исследований были определены три главных приоритета:

Таблица 1.

Перечень требуемых параметров при проектировании NINO-чипа для системы считывания времяпролетного детектора ALICE TOF

| Параметр | Значение | Примечание |

|---|---|---|

| Входные параметры: | ||

| емкость детектора, пФ | 10 | |

| максимальный сигнал, пКл | 1.5 | |

| импеданс линии связи с детектором, Ом | 55 | |

| длина линии связи с детектором, Ом | >20 | Две линии по 110 Ом в параллель |

| Требуемые параметры чипа: | ||

| время нарастания фронта, пс | ~ 500 | 1-й приоритет |

| входное дифференциальное сопротивление, Ом | 35–75 | |

| уровень ограничения, пКл | >100 | |

| коэффициент преобразования, мВ/фКл | 1000 | |

| эквивалентный шумовой заряд | 5000e | 2-й приоритет |

| собственный джиттер, пс | <50 | Суммарно с камерой |

| временной сдвиг, пс | <500 | |

| потребляемая мощность на канал, мВт | 30 | 3-й приоритет |

| порог регистрации, фКл | 5−50 | Внешнее управление |

| входное сопротивление, Ом | 55 | |

| выходной интерфейс | LVDS | Возможность перенастройки |

− первый − время сбора сигнала меньше 1 нс, что соответствует частотному спектру около 500 МГц;

− второй − уровень эквивалентного шумового заряда меньше 5000 электронов;

− третий − уровень рассеиваемой мощности 30 мВт на канал.

Процессу постановки задачи на проектирование предшествовал расчет параметров принципиальной электрической схемы в системе проектирования CADENCE PSPICE в библиотеке элементов выбранной технологии IBM CMOS 0.25 мкм, представленной производителем. Часто считают этап PSPICE-моделирования следующим за формулированием основных свойств СИМС, но в данном случае расчет предшествовал детальной постановке задачи. На разных этапах ее постановки проводились дополнительные исследования прототипов и соответствующие им расчеты PSPICE-модели для максимальной конкретизации и коррекции исходных требований технического задания. Требование получения минимального временного джиттера проектируемой СИМС определило частотную полосу в 500 МГц и минимальное значение белого шума 5000е [3]. На основе расчета по эмпирической формуле σt = (N/A)tr (где N, В – величина белого шума, A, В − амплитуда сигнала, ${{t}_{r}}$, c − время нарастания сигнала), а также измеренных параметров прототипов: N/A ~ ~ (1/50−1/100) и ${{t}_{r}}~$ = 5 ⋅ 10–10 с − получена оценка временного джиттера ${{\sigma }_{t}}$ ~ 5−10 пс при амплитуде сигнала на уровне двойного порога срабатывания.

NINO-чип структурно (рис. 3) представляет собой 8-канальный усилитель-дискриминатор: полностью дифференциальная структура с непосредственными связями между каскадами; трансимпедансными дифференциальными входами с регулировкой входного сопротивления и защитой диодами Шоттки; ТОТ-функцией преобразования заряда в ширину импульса с регулируемой длительностью; регулируемой величиной гистерезиса пороговой характеристики; со схемой выработки сигнала 8-ИЛИ; выходными каскадами, подстраиваемыми под различные стандарты, например в уровнях LVDS; внешней установкой величины общего порога на 8 каналов.

Рис. 3.

Вторая окончательная версия 8-канального NINO-чипа: слева – кристалл и наименования выводов; справа – схема разварки выводов NINO-чипа в корпусе ТАРР76.

На рис. 4 показана структурная блок-схема одного канала NINO-чипа.

Структурно NINO-чип состоит из предусилителя, четырехкаскадного дискриминатора, схемы растяжителя импульса, управляемого выходного каскада, схемы стабилизации характеристик, схемы управления гистерезисом и схемы выработки сигнала 8-ИЛИ.

Усиление А по напряжению входного предусилителя составляет ~30 при входном дифференциальном импедансе 55 Ом. Компаратор напряжения реализован в виде усилителя-ограничителя на четырех каскадах с полосой частот примерно 500 МГц и коэффициентом усиления А ~ 6 каждый и общим усилением А ~ 1000.

Все связи между каскадами реализованы гальваническими соединениями, исключающими возникновение дополнительных шумов и нежелательных переходных процессов за счет реактивного сопротивления переходных конденсаторов. Поэтому в конфигурацию входного каскада (см. рис. 4) включена схема стабилизации рабочих характеристик (ССРХ) по постоянному току, позволяющая поддерживать все основные параметры при изменениях порогового напряжения, подстройке входного импеданса схемы, температурном дрейфе и технологическом разбросе при массовом производстве.

Практически минимальная величина ~2 мВ постоянного смещения между дифференциальными входами каждого канала контролировалась на роботизированном стенде как один из основных критериев работоспособности NINO-чипа в процессе разбраковки конечной партии из 30 тыс. штук (240 тыс. контролируемых каналов).

Блок ССРХ поддерживает режим работы канала считывания по постоянному току, а также снижает уровень низкочастотных фликкер-шумов 1/F [5]. PSPICE-расчет шумов схемы и схемотехнические приемы позволили снизить приведенные ко входу шумы до величины 1900е при нулевой входной емкости [3]. Такое решение обеспечило компенсацию низкочастотной компоненты 1/F шумов, что положительно сказалось на способности достижения низких порогов, не меняя уровень белого шума, влияющего на величину временного джиттера.

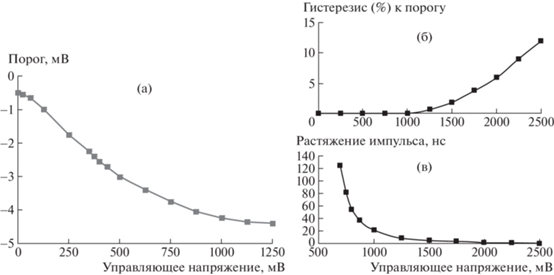

Еще одна новая функция добавлена в структуру NINO-чипа − это управляемый растяжитель длительности выходного импульса. Диапазон длительностей импульсов на выходе NINO-чипа без расширителя составляет 1−6 нс при среднем значении около 3 нс. Импульсы такой длительности трудно передать по скрученной паре проводов, даже на расстояние в несколько метров, кроме того, минимальная ширина импульса ограничена требованиями времяцифрового преобразователя. Например, для чипа HPTDC (High Precision Time To Digital Converter) [6] это значение составляет 6 нс. Практически в эксперименте при реальных длинах соединительных кабелей минимальную величину ширины импульса на входах HPTDC [6] устанавливают равной 10−15 нс. При этом результирующая ширина импульса на выходе NINO-чипа складывается из собственной длительности импульса плюс приложенная к заднему фронту добавочная величина, заданная расширителем. Добавочной длительностью можно управлять при помощи внешнего напряжения в широких пределах, от 1 нс до нескольких миллисекунд, как это показано на рис. 5. Формирование растянутого импульса осуществляется от заднего фронта исходного импульса для сохранения пропорциональности ширины импульса входному заряду, так как в NINO-чипе реализована функция преобразования заряда в длительность импульса по ТОТ (Time Over Threshold) методу.

Рис. 5.

Графики управления параметрами NINO-чипа: а − пороговая характеристика, б − гистерезис, в − длительность выходного импульса.

Для расширения возможностей применения NINO-чипа в его структуру была введена схема управления величиной гистерезиса пороговой характеристики в диапазоне 0−12% от величины порога. Все электронные усилители-дискриминаторы обязательно обладают хотя бы паразитным значением гистерезиса. Зависимость величины гистерезиса от управляющего напряжения показана на рис. 5. Медленно спадающие задние фронты импульсов могут содержать различные неоднородности, существенно влияющие на качественные характеристики ТОТ-метода. Это приводит к неоднозначности преобразования заряд−длительность. Данная проблема пороговых схем традиционно решается, в том числе введением гистерезиса.

ПОРОГОВАЯ ХАРАКТЕРИСТИКА И НЕЛИНЕЙНОСТЬ

Пороговая характеристика − это зависимость эффективного порога срабатывания от внешнего управляющего напряжения, устанавливаемого на внешних выводах чипа. Практически пороговая характеристика показывает также линейный диапазон передаточного тракта усилителя-дискриминатора, и по ней можно определить общий коэффициент преобразования.

Как видно из рис. 5, пороговая характеристика нелинейная, а линейный участок наблюдается лишь в начале характеристики. На первый взгляд, нелинейность − существенный недостаток, но на практике является преимуществом. Мягкое последовательное ограничение в каскадах усилителя-ограничителя не порождает гармоник высоких порядков и снижает помехи выходного каскада на вход, а также перекрестные межканальные помехи через внутренние цепи NINO-чипа. Это неочевидное положительное качество было изучено на первой экспериментальной версии NINO-чипа, которая содержала выводы схем управления каскадами усиления. Эта возможность была использована также для измерения шумов схемы и определения пределов устойчивости усилительного тракта с общим усилением около 1000 при перераспределении усиления между каскадами в различных пропорциях.

Разработка NINO-чипа началась в 2002 г. и завершилась в 2004 г. Произведено 30 000 чипов по технологическому процессу IBM CMOS 0.25 мкм. Был выбран 76-контактный корпус ТАРР76 с двухрядным расположением контактов, размер которых составляет 300 × 300 мкм с шагом 500 мкм (рис. 3). Запайка NINO-чипа в корпусе ТАРР76 (рис. 2) осуществлялась, как обычного компонента поверхностного монтажа.

Разработка NINO-чипа велась из расчета обеспечения требуемых параметров полосы частот и, соответственно, временного разрешения чипа, основанного на опыте построения и измерениях прототипов, что позволило избежать попыток достичь рекордных значений, но остаться в пределах минимального технологического разброса процесса IBM CMOS 0.25 мкм. Основные характеристики NINO-чипа представлены в табл. 2.

Таблица 2.

Результаты измерений основных параметров NINO-чипа

| Параметр | Условия | Мини-мальный | Типовой | Макси-мальный |

|---|---|---|---|---|

| Входные параметры | ||||

| Входное напряжение смещения, В | Rу = 20, 25, 37 Ом | 0.4 | 0.85 | 1.2 |

| Дифференциальное напряжение смещения, мВ | <2 | |||

| Диапазон порогов, фКл | 10−500 | |||

| Входная емкость, пФ | ~1 | |||

| Входное дифференциальное сопротивление, Ом | Rу = 20, 25, 37 Ом | 35 | 50 | 74 |

| Уровень ограничения, фКл | >200 | |||

| Усилительные параметры | ||||

| Коэффициент преобразования заряд в напряжение, мВ/фКл | Cдет = 0 пФ | 1080 | ||

| Преобразование заряд к порогу, мВ/фКл | Cдет = 0 пФ | 4 | ||

| Эквивалентный шумовой заряд, e/фКл | Uраст = 1.3 В | 1900/0.25 | ||

| Коэффициент преобразования, разброс, % | Uhyst = 0 В | <10 | ||

| Выходные параметры | ||||

| Диапазон выходных токов, мА | 1−6 | |||

| Диапазон растяжения импульса, нс | Uраст = 2.5–0.7 В | 0−100 | ||

| Типовая длительность импульса, нс | Uраст = 1.3 В | 15 | ||

| Разброс длительности импульса, % | Uраст = 1.3 В | 10 | ||

| Тип выхода | Токовый ключ | LVDS | ||

| Тип выхода ИЛИ | Токовый ключ | LVDS | ||

| Динамические свойства | ||||

| Малосигнальный спектр, МГц | −3 дБ | ~500 | ||

| Время нарастания переходной характеристики, пс | 10−90% | 600 | ||

| Минимальная длительность входного импульса, нс | Uраст = 2.5 В | ~0.6 | ||

| Диапазон длительности выходного импульса, нс | Uраст = 2.5 В | 1–6 | ||

| Собственный временной джиттер, пс | Qвх > 200 фКл | 6 | ||

| Гистерезис, диапазон, % | 0−12 | |||

| Питание | ||||

| Диапазон напряжения питания, В | 2.2 | 2.5 | 5.5 | |

| Ток потребления на один канал, мА | 11.9 | 14.4 | 38.1 | |

| Ток потребления на чип, мА | 95 | 115 | 305 | |

| Потребление на чип, мВт | 288 | |||

| Потребление на один канал, мВт | 36 | |||

| Взаимовлияние каналов, дБ | –50 | |||

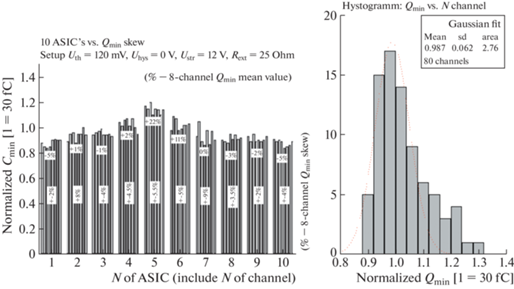

Контроль параметров NINO-чипов из массовой партии в 30 тыс. штук проводился на десяти случайно выбранных экземплярах. Измерялась минимальная величина заряда при фиксированном пороге. Измерение осуществлялось при следующих условиях: управляющее напряжение порогом 120 мВ (соответствует 10 фКл), величина гистерезиса 0%, управляющее напряжение растяжителем +1.2 В (соответствует длительности около 12 нс), значение входного импеданса 25 Ом. Результаты исследований показаны на рис. 6, где изображены две гистограммы основного параметра − зависимости эффективности срабатывания при минимальном заряде на входе от номера чипа и канала внутри. Согласно гистограммам, средний разброс минимального значения порога по 80-ти каналам составил 6.2%, средний разброс по чипам – 6.8%, разброс 8-ми каналов внутри чипа − 5.7%.

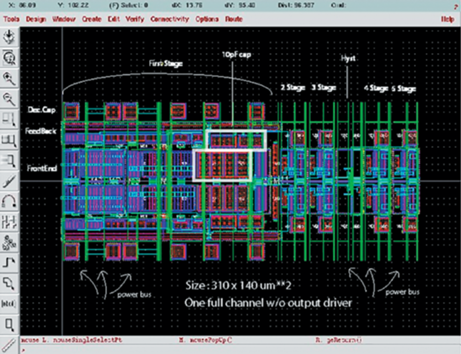

ТОПОЛОГИЯ КРИСТАЛЛА NINO-ЧИПА

На основе статистических данных измерений пороговых характеристик NINO-чипа можно сделать вывод, что разброс основных свойств NINO-чипов не оказывает существенного влияния на параметры проектируемой системы считывания.

8-канальный усилитель-дискриминатор NINO состоит из покаскадно независимых по цепям питания и общего провода (“земля”) частей. По горизонтали чип (рис. 7) разделен на аналоговую и цифровую части с раздельными выводами аналоговой “земли” и питания и цифровой “земли” и питания. Это необходимо для обеспечения устойчивости и минимального взаимовлияния каналов, так как общий коэффициент усиления около 1000 создает условия для паразитной связи с выхода на вход по внутренним цепям схемы. По вертикали 8 каналов чипа сгруппированы по два для подключения к внешним цепям “земли” и питания. Цепи общего провода (“земли”) каждого из восьми каналов имеют индивидуальный вывод для их объединения снаружи корпуса. Всего NINO‑чип содержит 4 вывода аналогового питания VDD_A, 10 выводов цифрового питания VDD_D, 10 аналоговых выводов “земли” GND_A и 7 выводов цифровой “земли” GND_D. Меры по снижению взаимовлияния каналов внутри чипа и разделение выводов корпуса обеспечили изоляцию каналов величиной 1/170.

PADI-ЧИП ДЛЯ ВРЕМЯПРОЛЕТНЫХ КАМЕР RPC − БЛИЗКИЙ ФУНКЦИОНАЛЬНЫЙ АНАЛОГ NINO-чипа

Обычно специализированные чипы не имеют близких аналогов и сравнивать их не с чем. Но недавно закончилась разработка очередной версии PADI СИМС [7, 8], выполненной по CMOS-технологии 0.13 мкм. PADI − близкий аналог NINO-чипа, который также разрабатывался для времяпролетных камер RPC в эксперименте CBM (GSI, Darmstadt). Интересно провести сравнение этих чипов.

Разработка PADI ведется с 2005 г. по настоящее время и, естественно, основана на опыте работ по NINO-чипу, однако использована более поздняя CMOS-технология 0.13 мкм, сулившая определенные преимущества.

В качестве одного из прототипов при разработке PADI служила накамерная электроника камер RPC [4] эксперимента FOPI (GSI, Darmstadt), которая была реализована на усилителе с полосой 1.5 ГГц и использовала традиционный принцип измерения амплитуды в АЦП и специальный аналоговый выход. Вторым прототипом являлся NINO-чип, разработка которого была завершена в ЦЕРН к 2005 г.

Очень важно понять мотивацию разработчиков PADI – вот что они пишут: “Мы протестировали NINO и наш дискретный прототип [4] и обнаружили сопоставимые результаты. Также стало очевидно, что СИМС позволяет достичь снижения потребляемой мощности, но меньшей пропускной способности, чем дискретные классические схемы, для которых могут быть выбраны наилучшие доступные дискретные интегральные схемы”. Таким образом, несмотря на результаты сравнения, выводы были сделаны достаточно парадоксальные. В результате постановка задачи на проектирование PADI приобрела определенную тенденциозность в желании превысить параметры NINO-чипа:

− уменьшить временной джиттер,

− снизить минимальный порог срабатывания,

− ввести поканальную регулировку порогов,

− расширить диапазон подстройки входного импеданса,

− ввести дополнительный аналоговый выход.

К сожалению, неоправданность установок, отсутствие расчетов PSPICE-моделей перед постановкой задач и тенденциозность поставленных задач привели к грубым ошибкам и, в свою очередь, в целом к неверной постановке задачи на проектирование PADI.

Формально и структурно при этом PADI и NINO-чипы достаточно близки. PADI представляет собой 8-канальный усилитель-дискриминатор с:

− трансимпедансными дифференциальными входами,

− регулируемой величиной входного сопротивления,

− дополнительными аналоговыми выходами для соединения с АЦП,

− опционно с наличием ТОТ-функции и ограниченным функционалом,

− схемой выработки сигнала 8-ИЛИ, выходными каскадами в стандарте LVDS,

− установкой порога только через цифровой протокол SPI.

Структурная схема PADI, показанная на рис. 8, содержит те же элементы, что и NINO-чип, с отличием в частностях, которые будут описаны ниже, но главное отличие − аналоговый выход каждого канала для передачи сигнала в АЦП. Это основная функциональная особенность PADI, что требует наличия АЦП. Отсутствие растяжителя длительности импульса ограничивает выбор типа ВЦП и в целом создает дополнительные проблемы реализации ТОТ-функции. В паре с PADI предполагается использовать специально разработанный для него ВЦП GET4 [9] (GSI, Darmstadt), представляющий собой 4-канальный чип ВЦП, разработанный в Германии и имеющий 25 пс на отсчет. По многим причинам, основные из которых − высокая склонность к самовозбуждению и неуниверсальность, PADI имеет ограниченное применение.

Рис. 8.

Структурное построение PADI: а − структурная схема предусилителя, б − структурная схема дискриминатора.

Более детальное сравнение основных параметров NINO- и PADI-СИМС дает табл. 3.

Таблица 3.

Сравнительные характеристики основных параметров NINO- и PADI-СИМС

| Основные параметры | NINO-СИМС (ALICE) | PADI-СИМС (GSI) |

|---|---|---|

| Число каналов в чипе | 8 | 8 |

| Технологический процесс | CMOS 0.25 мкм | CMOS 0.13 мкм |

| Коэффициент преобразования, мВ/фКл | 1080 | 1900 |

| Полоса частот предусилителя, МГц | 500 | 410 |

| Усиление предусилителя, В/В | 30 | 250 |

| TOT-функция | Да | Ограничено |

| Растяжитель длительности | Да | нет |

| Входное напряжение смещения, мВ | 2 | 1 |

| Эквивалентный шумовой заряд (e RMS) | 1750 | 1150 |

| Входной импеданс, Ом | 35−75 | 30−160 |

| Потребляемая мощность, мВт/канал | 27 | 17 |

| Перекрестные помехи | 1/200 | Нет данных |

| Установка порога | Аналоговая внешняя, общая | Встроенный ЦАП, поканальная |

| Собственный временной джиттер, пс | ~6 | ~6 |

| Напряжение питания, В | 2.5 | 1.5 |

| Выходные уровни | Настраиваемые, в том числе LVDS | LVDS |

В целом чипы имеют одно предназначение и в этом смысле похожи и близки по параметрам. Отличие в функциональности имеет значение для реализации конкретных систем считывания на основе того или иного чипа и может быть серьезно ограничено для PADI.

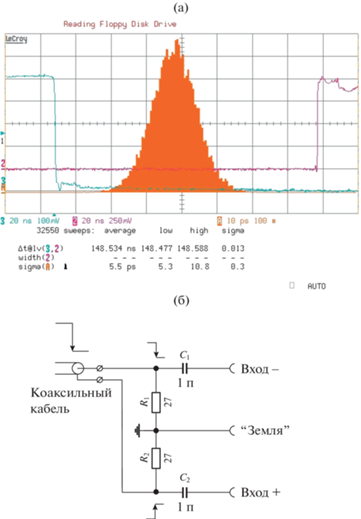

Собственный джиттер обоих чипов пренебрежимо мал (~6 пс), что подтверждается близкими значениями полосы частот и уровня собственных шумов. Величина джиттера имеет первостепенное значение при оценке качества времяпролетного чипа, а прецизионные временные измерения при помощи генератора импульсов с фронтами 250 пс и цифрового осциллографа с 40−80 ГФл представляет немалые сложности. На рис. 6 величина джиттера ~6 пс измерена с использованием осциллографа LeCroy (40 ГФл, 2 ГГц аналогового тракта) с собственным джиттером менее 5 пс и генератора с длительностью фронта 250 пс при величине входного заряда Qвх = 100 фКл и использовании дифференциального адаптера (рис. 9), специально предназначенного для точных временных измерений. Для считывания парафазного выхода в осциллографе использовался активный дифференциальный щуп LeCroy с полосой частот 1 ГГц.

Рис. 9.

Гистограмма измерения джиттера NINO-чипа (а) и схема дифференциального адаптера для точных временных измерений (б).

Важным качеством аналогового чипа является его устойчивость, особенно в составе многоканальной системы. Для PADI это известная проблема, которая обусловлена, вероятно, неоправданно большим значением коэффициента преобразования (250) в широкой полосе частот 410 МГц, а также наличием дополнительного широкополосного аналогового выхода, который полезен только для полноспектрального анализа сигнала с камеры. Его использование в многоканальном чипе оказалось неоправданным.

Длительный период времени разработки PADI (2005–2018 гг.) обусловлен трудностями в преодолении проблем, заложенных в постановке задачи и связанных с устойчивостью тракта, переходными помехами, внутренней структурой чипа.

Нет данных о величине перекрестной помехи PADI, которая также зависит от коэффициента усиления предусилителя 250 и оценочно должна быть в разы больше, чем ~1/200 у NINO-чипа, коэффициент усиления предусилителя которого равен 30.

Все вышеперечисленные особенности PADI определяют его ограниченное применение по сравнению с функционально более развитым NINO-чипом.

ВЫВОДЫ

При проектировании нового чипа принципиальное значение имеет правильная расстановка приоритетов, чтобы достижение одних параметров не противоречило другим. На практике часть требований к постановке задачи на проектирование PADI оказалась вовсе нереализуема.

Так, снижение джиттера возможно было при уменьшении времени нарастания сигнала и величины белого шума, однако одновременное увеличение коэффициента усиления в предусилителе сделало это невозможным. Даже переход к более совершенной CMOS-технологии 0.13 мкм против 0.25 мкм, хотя и обеспечил рост полосы частот единичного усиления примерно в 2 раза, но соотношение усилений 250/30 ~ 7 перекрыло прирост. Более точные измерения временного джиттера (см. рис. 9) обоих чипов показали необоснованность этой задачи.

Снижение минимального порога по сравнению с NINO-чипом также оказалось недостижимым по причине неустойчивости канала. При этом, хотя шумовые свойства чипов близки с точностью до методики измерения, но в 7 раз больший коэффициент преобразования создал для PADI проблемы и с минимально достижимым порогом считывания, и с устойчивостью в целом.

Регулировка порогов для каждого канала не обоснована, так как при 100%-ной эффективности регистрации их поканальная подстройка не требуется.

Введенный в состав PADI аналоговый выход создал основные проблемы с устойчивостью, и в последней шестой версии PADI-8 от него отказались, сохранив лишь в одном из восьми каналов в качестве рудимента.

При этом были отвергнуты те свойства NINO-чипа как прототипа, которые обеспечивали его многофункциональность: расширитель выходного импульса ТОТ-функции, универсальный выходной каскад и гистерезис пороговой характеристики.

В 2021 г. появилась публикация [10] о новой версии PSPICE-модели PADI. В ней нет ничего принципиально нового. В целом начиная с 2005 г. идеология PADI не менялась, продолжались попытки преодолеть ошибки в постановке задачи, не меняя саму постановку задачи.

Справедливо будет указать незавершенность разработки NINO-чипа. В планах его следующей итерации было введение, наряду с основным временным каналом, отдельного амплитудного канала с интегрированием входного сигнала для расширения функциональности ТОТ-метода и объединение временного и амплитудного каналов в один результирующий импульс. В данном случае создание NINO обогнало развитие ТОТ-методики.

При этом создатели PADI не имели опыта работы с ТОТ-методом, и не ставили себе задачу внедрения последних достижений в реализацию ТОТ-метода, а лишь рассматривали его как дополнительную опцию.

Список литературы

Toker O., Masciocchi S., Nygard E., Rudge A., Weilhammer P. // Nucl. Instrum. and Methods A. 1994. V. 340. P. 572. https://doi.org/10.1016/0168-9002(94)90140-6

Giannini F., Limiti E., Orengo G., Cardarelly R. // Nucl. Instrum. and Methods A. 1999. V. 432. P. 440. https://doi.org/10.1016/S0168-9002(99)00376-9

Anghinolfi F., Jarron P., Martemyanov A.N., Usenko E., Wenninger H., Williams M.C.S., Zichichi A. // Nucl. Instrum. and Methods A. 2004. V. 533. P. 183. https://doi.org/10.1016/j.nima.2004.07.024

Ciobanu M., Herrmann N., Hildenbrand K.D., Kiš M., Schüttauf A., Flemming H., Deppe H., Löchner S., Frühauf J., Deppner I., Loizeau P-A., Träger M. // IEEE Trans. Nucl. Sci. 2007. V. 54. Issue 4. P. 1201. https://doi.org/10.1109/TNS.2007.903186

Art Kay. Operational Amplifier Noise: Techniques and Tips for Analyzing and Reducing Noise. 1st Edition. Newnes: January 27, 2012.

Christiansen J. HPTDC High Performance Time to Digital Converter for HPTDC version 1.3. Version 2.2. CERN/EP – MIC, March 2004.

Ciobanu M., Herrmann N., Hildenbrand K.D., Kiš M., Schüttauf A. // 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC). 2009. P. 401. https://doi.org/10.1109/NSSMIC.2008.4774801

Ciobanu M., Herrmann N., Hildenbrand K.D., Kiš M., Schüttauf A., Flemming H., Deppe H., Löchner S., Frühauf J., Deppner I., Loizeau P.A., Träger M. // IEEE Trans. Nucl. Scie. 2014. V. 61. Issue 2. P. 1015. https://doi.org/10.1109/TNS.2014.2305999

Deppe H., Flemming H. // 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC). P. 295. https://doi.org/10.1109/NSSMIC.2009.5401741

Ciobanu M., Marghitu O., Constantinescu V., Herrmann N., Andersson H., Wieser M., Flemming H., Deppe H., Löchner S., Frühauf J., Deppner I., Loizeau P.A. // IEEE Trans. Nucl. Sci. 2021. V. 68. Issue 6. P. 1325. https://doi.org/10.1109/TNS.2021.3073487

Дополнительные материалы отсутствуют.

Инструменты

Приборы и техника эксперимента