Автоматика и телемеханика, № 2, 2022

Управление в технических системах

© 2022 г. И.А. СОКОЛОВ, д-р техн. наук (ISokolov@ipiran.ru),

Ю.А. СТЕПЧЕНКОВ, канд. техн. наук (YStepchenkov@ipiran.ru),

Ю.В. РОЖДЕСТВЕНСКИЙ, канд. техн. наук (YRogdest@ipiran.ru),

Ю.Г. ДЬЯЧЕНКО, канд. техн. наук (diaura@mail.ru)

(Федеральный исследовательский центр

“Информатика и управление” РАН, Москва)

ПРИБЛИЖЕННАЯ ОЦЕНКА ЭФФЕКТИВНОСТИ СИНХРОННОЙ

И САМОСИНХРОННОЙ МЕТОДОЛОГИЙ В ЗАДАЧАХ

ПРОЕКТИРОВАНИЯ СБОЕУСТОЙЧИВЫХ

ВЫЧИСЛИТЕЛЬНО-УПРАВЛЯЮЩИХ СИСТЕМ1

Статья посвящена сравнительному анализу эффективности исполь-

зования синхронной и самосинхронной (СС) методологий при проек-

тировании сбоеустойчивых вычислительно-управляющих систем в бази-

се комплементарной металл-диэлектрик-полупроводник (КМДП) техно-

логии. Подробно рассматриваются вопросы сбоеустойчивости техниче-

ских средств управления на примерах цифровых схем различного ти-

па. Подтверждено значительное увеличение времени бессбойной работы

(в 1,2-1,8 раза) СС-схем в сравнении с синхронными аналогами. Выделе-

ны наиболее существенные особенности СС-схемотехники, обеспечиваю-

щие повышение сбоеустойчивости СС-систем. Предложены схемотехниче-

ские методы повышения сбоеустойчивости СС-систем управления, увели-

чивающие время бессбойной работы комбинационных СС-схем до 4,0 раз

и последовательностных СС-схем до 7,1 раза.

Ключевые слова: технические средства, сбоеустойчивость, логический

сбой, синхронная схема, самосинхронная схема, парафазный сигнал,

C-элемент, индикация.

DOI: 10.31857/S0005231022020088

1. Введение

Решение практических задач вычислительного типа и управления сопря-

жено с обработкой большого объема данных в течение длительного времени.

С увеличением времени работы растет и риск логического сбоя в технических

средствах вычислительно-управляющей системы из-за меняющихся условий

эксплуатации и воздействия неблагоприятных факторов. Поэтому техниче-

ские средства вычислительно-управляющих систем должны быть эффектив-

но устойчивыми к логическим сбоям.

1 Исследование финансово поддержано Министерством науки и высшего образования

Российской Федерации (проект № 075-15-2020-799).

122

Интенсивность возникновения сбоев в цифровых схемах на несколь-

ко порядков превышает величину интенсивности возникновения отказов

(∼ 10-4 1/ч против ∼ 10-7 1/ч для серийно выпускаемых микропроцессор-

ных кристаллов [1]). По мнению авторов публикации [1]: “Создание новейших

технологий и методов повышения выхода годных сверх больших интеграль-

ных схем (СБИС) позволяет предполагать усугубление имеющегося разрыва

и, как следствие, выделение сбоев в преобладающий фактор, определяющий

надежность” цифровых схем. Повышение сбоеустойчивости вычислительных

комплексов возможно за счет использования аппаратных методов контроля

их работоспособности и саморемонта. Наиболее выгодной в этом отношении

является самосинхронная (СС) методология [2-5].

Null Convention Logic (NCL) схемы [5] являются одним из хорошо извест-

ных подклассов СС-схем. NCL-схемы используют парафазные входы, выходы

и внутренние сигналы с нулевым спейсером. Базовая библиотека ячеек для

проектирования NCL-схем включает всего лишь 29 так называемых много-

пороговых элементов, каждый из которых индицирует все свои входы. Это

свойство является “ноу-хау” NCL-методологии и упрощает проектирование

нечувствительных к задержке СС-схем. К недостаткам этой методологии сле-

дует отнести значительную аппаратную избыточность и связанное с ней по-

вышенное энергопотребление [6].

Есть и другие подходы к проблеме сбоеустойчивости технических средств

вычислительно-управляющих систем [7-9]. В публикации [7] предлагается

метод макро-синхронного микро-асинхронного конвейера (MSMA) с исполь-

зованием устойчивой к логическим сбоям и маломощной версии асинхрон-

ной NCL-схемы. Однако это решение не является СС-схемой. В [8, 9] описан

трехъядерный процессор ARM Cortex-R5 с синхронизацией шага (TCLS). Ар-

хитектура TCLS включает три центральных процессора (ЦП) и обеспечива-

ет надежность на системном уровне. Предлагаемое решение предполагает,

что “отдельные ЦП не обязательно должны быть сбоеустойчивыми и могут

быть реализованы с использованием коммерческого технологического про-

цесса” [8]. Однако все рассмотренные публикации не дают количественных

оценок уровня сбоеустойчивости реальных продуктов.

Подход, предлагаемый в [2, 3], решает обозначенную проблему. Под-

ход основывается на сбоеустойчивой СС-парадигме, позволяющей исполь-

зовать широкую номенклатуру библиотечных ячеек, унарное и бифазное

избыточное кодирование сигналов в дополнение к парафазному кодиро-

ванию. Использование разнотипного кодирования обеспечивает разработ-

ку СС-схем, более простых по сравнению с NCL-аналогами. Сбоеустойчи-

вая СС-методология обеспечивает сохранение работоспособности техниче-

ских средств вычислительно-управляющего комплекса, построенного на этом

базисе, в широком диапазоне напряжения питания и температуры окружаю-

щей среды, обнаружение и локализацию константных неисправностей, воз-

никающих из-за неблагоприятных воздействий, в том числе радиационных

факторов, повышение срока бессбойной работы.

123

Из-за наличия глобального тактового дерева синхронные схемы часто вос-

принимают логический сбой как отказ и требуют использования чрезмерной

аппаратной избыточности для парирования таких сбоев. СС-схемы, благода-

ря изначальной аппаратной избыточности и двухфазному функционирова-

нию, способны отличить кратковременный логический сбой от отказа. Кроме

того, они имеют более высокий естественный уровень сбоеустойчивости, чем

их синхронные аналоги.

Цель статьи получить приближенную оценку эффективности СС-мето-

дологии для проектирования технических средств вычислительно-управляю-

щих систем, работающих в условиях воздействия дестабилизирующих фак-

торов и устойчивых к кратковременным логическим сбоям.

В данной статье анализируется устойчивость цифровых схем к кратко-

временным логическим сбоям, длительность которых составляет от сотен

пикосекунд до единиц наносекунд [10]. В комбинационных схемах они са-

моликвидируются, но в схемах с памятью (триггерах, регистрах) сбой мо-

жет инвертировать хранимый бит информации и стать постоянным. Статья

не рассматривает выносные и подменные типы логических сбоев [2], веро-

ятность появления которых в практических СС-схемах чрезвычайно мала.

Термин “сбоеустойчивость” трактуется как способность технической системы

продолжить корректное функционирование без остановки с помощью маски-

рования логического сбоя или после некоторой задержки, связанной с ожи-

данием самоликвидации сбоя без порчи обрабатываемых данных.

2. Сравнение классических синхронных и СС-реализаций

Проектирование и изготовление технических средств вычислительно-

управляющих систем предполагают их корректное функционирование в за-

данных условиях эксплуатации в течение определенного временного интер-

вала в условиях внешней среды с оговоренным уровнем плотности сбоев.

Практически всегда это оптимизационная задача, минимизирующая кри-

терий “риск-стоимость” при заданных ограничениях на условия эксплуата-

ции и требуемые технические характеристики. Одним из способов достиже-

ния оптимального результата в решении этой задачи является использование

СС-методологии.

Самосинхронная методология предполагает полный контроль завершения

переключения всех элементов схемы, изменение состояния выходов кото-

рых было инициировано текущим набором входных данных [2]. Подтвер-

ждение завершения переключения всех активных элементов схемы являет-

ся необходимым условием для начала обработки следующего набора. Этот

контроль выполняется специальными индикаторными схемами, собирающи-

ми полную информацию об окончании процесса обработки набора данных.

Взаимодействие СС-схем осуществляется на основе запрос-ответных отноше-

ний цифровых устройств в тракте обработки данных. Каждый функциональ-

ный СС-блок использует информацию от следующего СС-блока о его готов-

ности к обработке новых данных и формирует сигнал о завершении своей

124

a

VDD

QB

D

Q

clk

б

QB

D

& 1

1

&

&1&1

I

&1&

& 1

& 1

1 &

E

Q

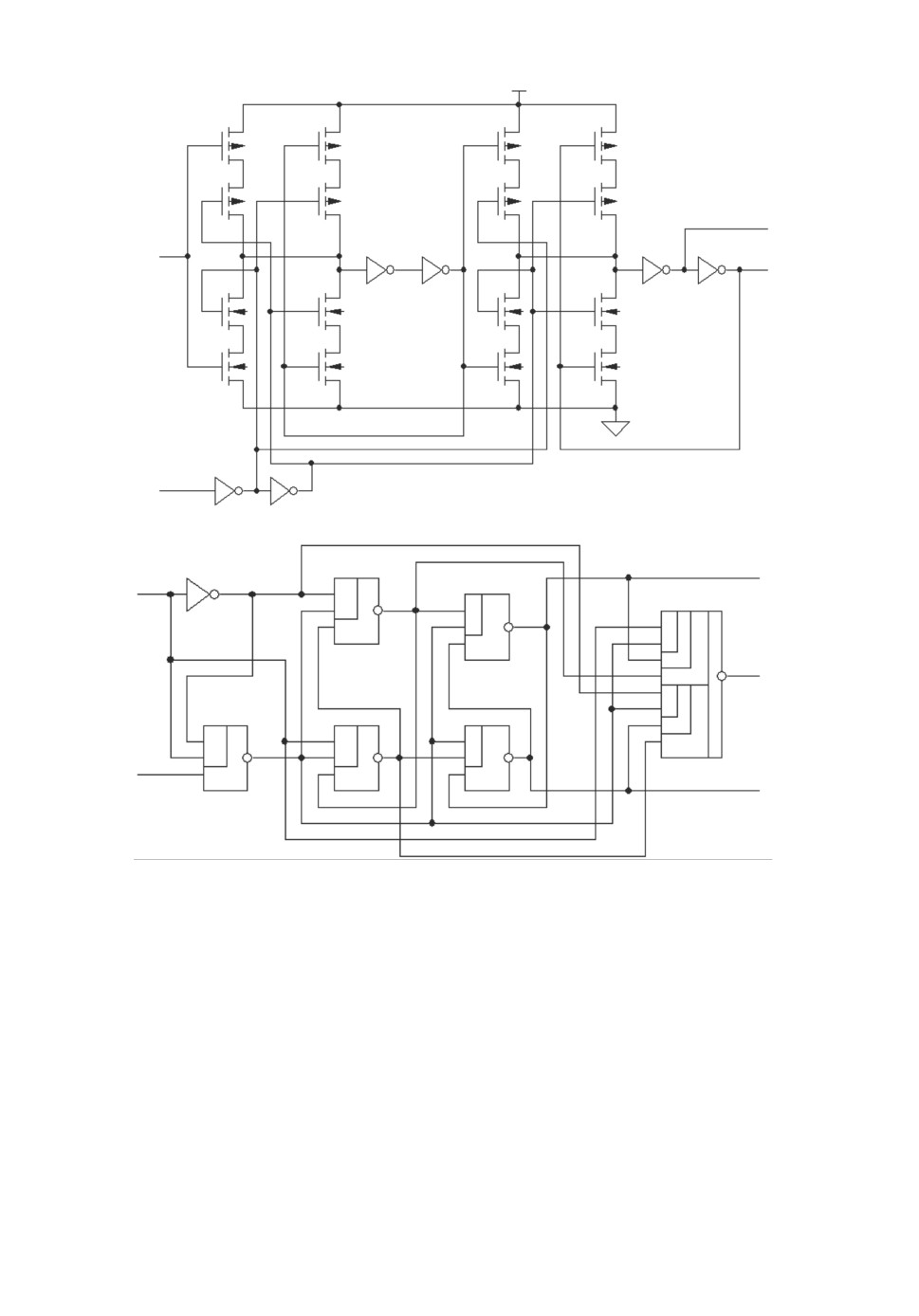

Рис. 1. D-триггер: а синхронная схема на КМДП-транзисторах; б СС-схема.

работы для предыдущего СС-блока. Для организации такого процесса обра-

ботки применяется специальное СС-кодирование данных [2].

Простейшим и наиболее распространенным СС-кодом является парафаз-

ный код, где информационный бит “0” представлен комбинацией “01”, инфор-

мационный бит “1” комбинацией “10”, и вводится специальное состояние

спейсер (“00” или “11”). Полный цикл работы схемы состоит из двух чередую-

щихся фаз рабочей и спейсерной.

Благодаря такой организации процесса обработки данных СС-схема при-

обретает следующие свойства, отличающие ее от синхронного аналога:

быстродействие, определяемое только задержками элементов схемы;

125

a

VDD

A

CI

B

S

CO

б

VDD

VDD

CO

AB

SO

BB

SO

1

A

SOB

SOB

AB

CIB

NOR2

C

Ind

CIB

СO

1

CI

VDD

СOB

BB

NOR2

B

COB

A

B

CI

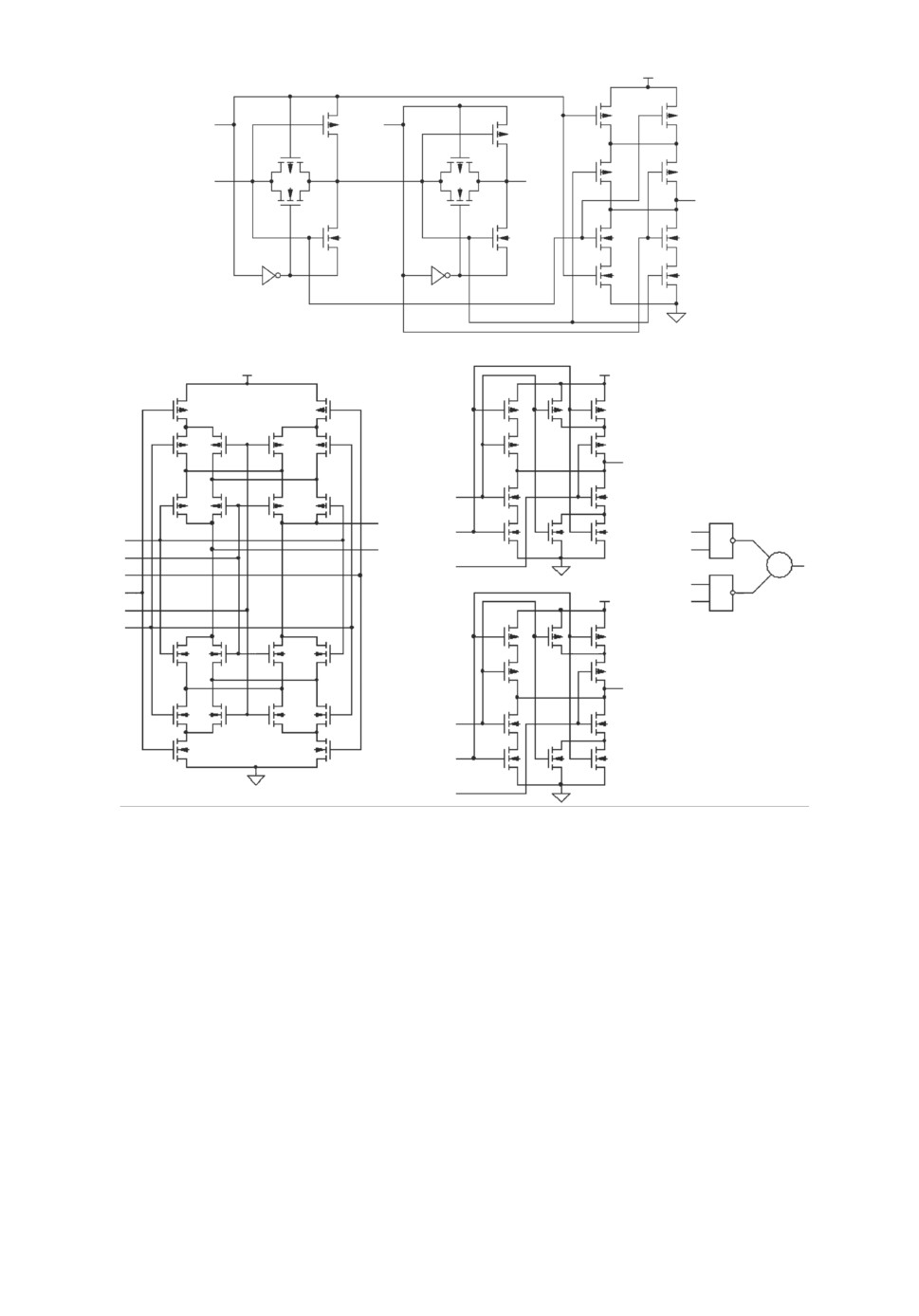

Рис. 2. Двоичный сумматор: а синхронная схема; б СС-схема.

естественную стопроцентную самопроверяемость и самодиагностируе-

мость по отношению к множественным константным неисправностям;

безопасность работы на основе бестестовой локализации неисправно-

стей;

максимально возможную область эксплуатации, определяемую только

физическим сохранением переключательных свойств активных элементов [3].

К недостаткам СС-схемотехники следует отнести аппаратную избыточ-

ность СС-схем по отношению к синхронным аналогам из-за избыточного ко-

дирования сигналов и наличия индикаторной подсхемы. Сложность СС-схем

оказывается больше сложности синхронных аналогов до 1,7 раза для схем с

памятью и до 3,0 раза для комбинационных схем. Рисунок 1 демонстрирует

примеры реализации D-триггера в синхронном (рис. 1,а) и СС (рис. 1,б ) ис-

полнении. СС-схема триггера содержит в 1,7 раза больше комплементарных

126

VDD

I1

I0

Y

Рис. 3. Принципиальная схема С-элемента.

X

C

Y

=1

I

XB

C

YB

E

Рис. 4. Разряд СС-регистра хранения на С-элементах.

металл-диэлектрик-полупроводник (КМДП) транзисторов, чем синхронный

аналог. В значительной степени это объясняется наличием в схеме индика-

торного элемента, формирующего выход I.

Рисунок 2 показывает схемотехническую реализацию одноразрядного дво-

ичного сумматора в синхронном (рис. 2,а) и СС (рис. 2,б ) базисах. Схема

С-элемента, формирующего индикаторный выход сумматора, представлена

на рис. 3. Сложность СС-схемы сумматора в КМДП-транзисторах в 2,8 раза

больше сложности синхронной реализации.

Соотношение аппаратных затрат СС и синхронного аналога зависит от

типа схемы. В некоторых случаях сложность СС-схем сравнима с аппарат-

ными затратами синхронных аналогов. Например, разряд регистра хранения

в ступени СС-конвейера реализуется обычно на С-элементах (рис. 4) и имеет

такую же сложность, как и синхронный вариант.

Двухфазный характер работы СС-схем и наличие индикаторной подсхемы

снижают быстродействие примерно в два раза. Однако существуют методики,

позволяющие приблизить быстродействие ряда СС-схем к уровню синхрон-

ных аналогов [11].

Описанные выше свойства СС-схемы обеспечивают их естественную им-

мунность к логическим сбоям. Исследования показали [12, 13], что за счет

полноты парафазного кодирования информационных сигналов, когда состоя-

ние, противоположное спейсеру, индицируется как спейсер, двухфазной дис-

циплины работы и индицирования всех переключений элементов СС-схемы

устойчивы к 90% однократных кратковременных логических сбоев.

127

Однократность подразумевает появление сбоя лишь в одном логическом

элементе схемы. Схема элемента может состоять из нескольких КМДП-тран-

зисторов. Исследования показывают, что типовой эффективный диаметр тре-

ка ядерной частицы, вызывающей логический сбой, не превышает 2-2,5 мкм

[14]. В КМДП-технологии с проектными нормами 65 нм это соответствует

размеру стандартного элемента. Таким образом, физическая причина логи-

ческого сбоя обычно затрагивает сразу несколько транзисторов. Однако ве-

роятность появления сбоя пропорциональна площади топологической реали-

зации схемы, которая в свою очередь пропорциональна числу транзисторов

в схеме. Поэтому оценку уровня сбоеустойчивости схемы целесообразно про-

водить исходя из числа транзисторов в схеме.

При заданной плотности потока случайных событий, λin, инициирующих

однократные логические сбои, интенсивность сбоев (failure rate function) λ

для схемы определяется как сумма интенсивностей сбоев отдельных компо-

нентов (в данном случае транзисторов) [15, формула (3.11)]:

λ = N · λin · α,

где N - число транзисторов в схеме; α - вероятность сбоя при повреждении

одного транзистора. Поскольку время бессбойной работы обратно пропорцио-

нально интенсивности сбоев [15, формула (3.14)], отношение времен бессбой-

ной работы (failure-free operation time, FFOT) для СС-схемы и ее синхронного

аналога будет иметь вид:

λS

NS · λin · αS

αS

(1)

KFFOT =

=

=

,

λST

NST · λin · αST

AR · αST

где λS , λST - плотность потока сбоев синхронной и СС-схемы; NS , NST -

число транзисторов синхронной и СС-схемы; αS , αST - вероятность сбоя при

повреждении одного транзистора синхронной и СС-схемы; AR = NST /NS -

коэффициент аппаратной избыточности СС-схемы в сравнении с синхронным

аналогом.

Исследования, выполненные ранее [12, 13], позволили оценить вероятность

сбоя при повреждении одного транзистора синхронной и СС-схемы для ком-

бинационных (αS = 0,5, αST = 0,1) и триггерных (αS = 0,5, αST = 0,24) ти-

пов схем в предположении, что сбой одного транзистора вызывает сбой ло-

гического элемента. В комбинационных схемах AR = 2,8 и отношение времен

бессбойной работы СС и синхронного аналогов:

αS

0,5

(2)

KFFOTC1 =

=

≈ 1,8.

AR · αST

2,8 · 0,1

В последовательностных схемах AR = 1,7. Тогда для них:

αS

0,5

(3)

KFFOTS1 =

=

≈ 1,2.

AR · αST

1,7 · 0,24

Формулы (1)-(3) дают лишь приблизительную сравнительную оценку сбое-

устойчивости синхронных и СС-схем. Но они наглядно демонстрируют по-

вышение сбоеустойчивости СС-схем по сравнению с синхронными аналогами

даже несмотря на их аппаратную избыточность.

128

3. Повышение сбоеустойчивости СС-схем

Наиболее опасный тип логического сбоя в СС-схемах при парафазном со

спейсером кодировании информационных сигналов появление состояния

парафазного сигнала, противоположного спейсеру. Традиционная индикация

парафазного сигнала предполагает, что каждый парафазный сигнал имеет

только одно спейсерное состояние (“00” или “11”) и рассматривает любое, от-

личное от спейсера, состояние как рабочее. Поэтому и состояние, противо-

положное спейсеру (антиспейсер), будет проиндицировано как рабочее, что

приведет к распространению ошибки по схеме.

В [13] были предложены схемотехнические и топологические методы,

предотвращающие распространение антиспейсера по СС-схеме. Антиспейсер

индицируется как спейсер с помощью элемента “равнозначность” или “нерав-

нозначность”. Такое решение маскирует антиспейсер и повышает устойчи-

вость комбинационных СС-схем к однократным логическим сбоям до уров-

ня 95% (αST = 0,05).

Практические СС-схемы проектируются в виде конвейера, аналогично

синхронным схемам. Традиционно регистр хранения промежуточных резуль-

татов ступени конвейера реализуется на гистерезисных триггерах [2] (С-эле-

ментах Маллера [5]), поскольку они хранят и рабочее, и спейсерное состояние.

Антиспейсер на входе такого разряда регистра хранения записывается в него

в рабочей фазе, но индицируется как спейсер. С точки зрения дисциплины

работы СС-схемы, это не критично: индикатор регистра остается в спейсере,

и регистр ожидает смены антиспейсера на входе сбойного разряда рабочим

состоянием.

Однако антиспейсер внутри разряда регистра блокирует запись в раз-

ряд рабочего состояния по окончании логического сбоя, вызывая останов

СС-схемы. Схемотехнические методы, предложенные в [16, 17], обеспечива-

ют снятие этой блокировки. Они повышают сбоеустойчивость СС-регистра

до уровня 95,3% (αST = 0,047).

В результате применения специальных схемотехнических и топологиче-

ских методов повышения сбоеустойчивости СС-схем отношения времени бес-

сбойной работы СС-схем и их синхронных аналогов в формулах (2)-(3) су-

щественно улучшаются. Для схем комбинационного типа:

αS

0,5

KFFOTC2 =

=

= 4,0,

AR · αST

2,5 · 0,05

для схем последовательностного типа:

αS

0,5

KFFOTS2 =

=

≈ 7,1.

AR · αST

1,5 · 0,047

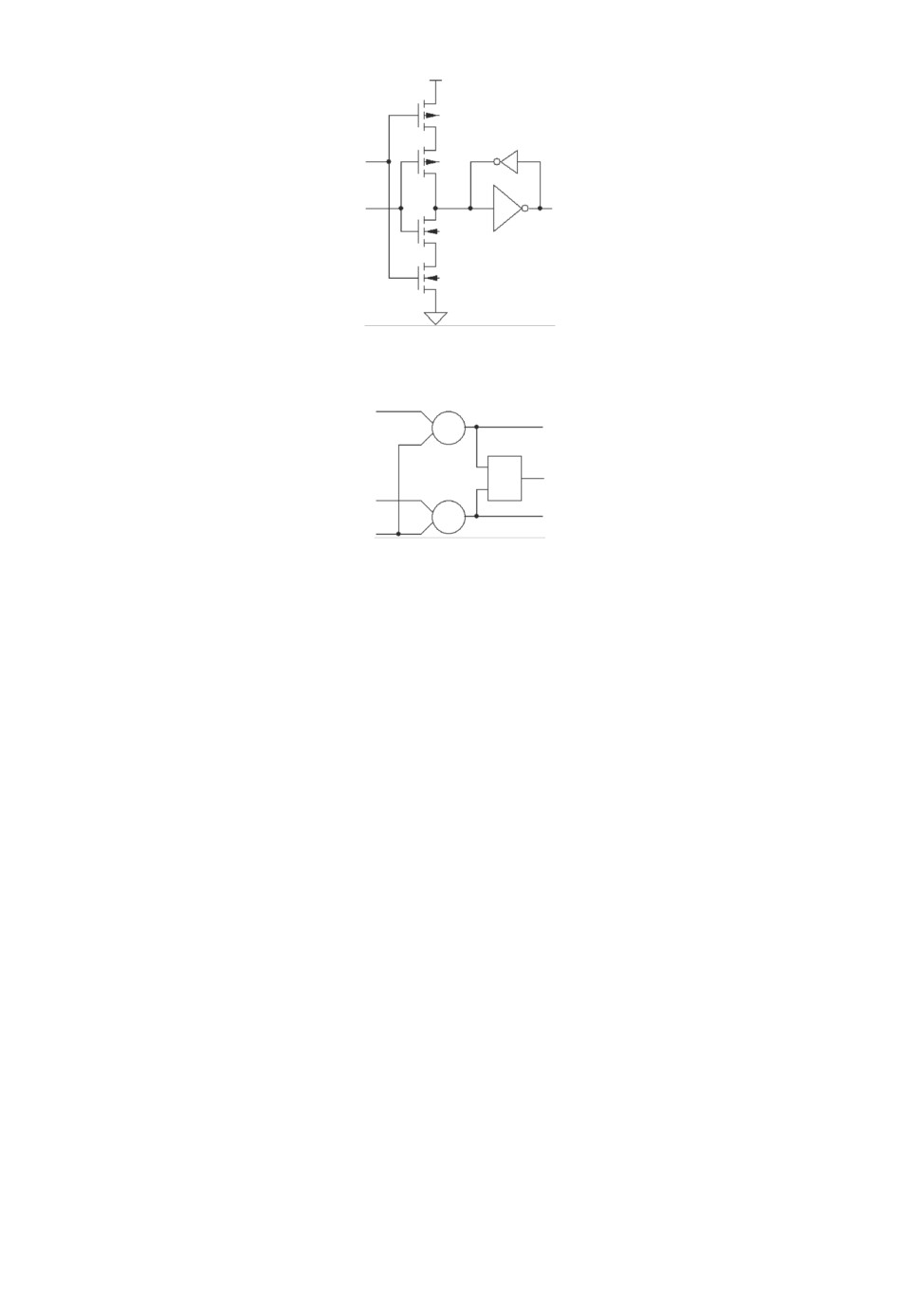

Устойчивость индикаторной подсхемы СС-схем к логическим сбоям повы-

шается за счет использования DICE-реализации С-элемента [18] с синфаз-

ными входами и выходом, которая маскирует логические сбои на входах и

внутри С-элемента.

129

Таким образом, СС-схемы обладают более высокой устойчивостью к ло-

гическим сбоям и бóльшим временем бессбойной работы по сравнению с син-

хронными аналогами как в минимальном, так и в сбоеустойчивом испол-

нении за счет более надежного маскирования одиночных логических сбо-

ев. В качестве примера оценим преимущество реального умножителя 54 × 54

в СС-исполнении. Варианты синхронного умножителя [19, таблица V] име-

ют сложность 78800, 81600, 82500 и 100200 КМДП-транзисторов. СС-умно-

житель с парафазной кодировкой сигнала [20] имеет сложность 218 000

КМДП-транзисторов. Следовательно, отношение времени безотказной рабо-

ты СС-умножителя и его аналогов находится в диапазоне от 3,6 до 4,6.

4. Заключение

Приближенные оценки показывают, что СС-методология проектирования

технических средств вычислительно-управляющих систем обеспечивает луч-

шую сбоеустойчивость, чем синхронная методология. Благодаря двухфазной

дисциплине работы и избыточному кодированию информационных сигна-

лов СС-схемы иммунны к 90% логических сбоев в комбинационной части и

76% сбоев в последовательностной части. За счет этого технические средства

вычислительно-управляющих систем, построенные на базе СС-методологии,

несмотря на свою аппаратную избыточность, обеспечивают большее время

бессбойной работы в сравнении с синхронными аналогами: в 1,8 раза в схе-

мах комбинационного типа и в 1,2 раза в последовательностных схемах.

Предложенные методы схемотехнического и топологического проектирова-

ния СС-схем увеличивают время бессбойной работы технических средств

вычислительно-управляющих систем в 2,2 раза для схем комбинационного

типа и до 5,8 раза для схем последовательностного типа.

Научная новизна данной статьи заключается в следующем:

она выполняет сравнительный анализ возможностей применения син-

хронной и СС-методологии для построения элементной базы высоконадеж-

ных технических средств вычислительно-управляющих систем;

она показывает, что применение СС-схемотехники обеспечивает более

высокий уровень устойчивости технических средств вычислительно-управ-

ляющих систем к однократным логическим сбоям, чем синхронные аналоги,

при сравнимых аппаратных затратах.

Дальнейшие направления работы связаны с исследованием аппаратных

решений, использующих помехоустойчивые свойства СС-кодов и отслежи-

вающих момент окончания логического сбоя, которые могут дать существен-

ный выигрыш в устойчивости технических средств вычислительно-управ-

ляющих систем к однократным сбоям.

СПИСОК ЛИТЕРАТУРЫ

1. Викторова В.C. Анализ надежности отказоустойчивых управляющих вычисли-

тельных систем / В.C. Викторова, Н.В. Лубков, А.С. Степанянц. М.: ИПУ РАН.

130

2.

Kishinevsky M., Kondratyev A., Taubin A., Varshavsky V. Concurrent Hardware:

the Theory and Practice of Self-Timed Design. N.-Y.: J. Wiley & Sons.

1994.

-

ISBN 978-0-471-93536-0.

3.

Zakharov V., Stepchenkov Y., Diachenko Y., Rogdestvenski Y. Self-Timed Circuitry

Retrospective // Int. Conf. Engineering Technologies and Computer Science (EnT).

4.

Tabassam Z., Naqvi S.R., Akram T., Alhussein M., Aurangzeb K., Haider S.A. To-

wards Designing Asynchronous Microprocessors: From Specification to Tape-Out //

IEEE Access. 2019. V. 7. No. 5. P. 33978-34003.

5.

Smith S.C., Jia Di. Designing Asynchronous Circuits using NULL Convention Logic

(NCL) // Synthesis Lect. on Digital Circuits and Syst. 2009. V. 4. No. 1. P. 61-73.

6.

Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гринфельд Ф.И., Филимонен-

ко О.П., Морозов Н.В., Степченков Д.Ю., Плеханов Л.П. Библиотека функцио-

нальных ячеек для проектирования самосинхронных полузаказных БМК мик-

росхем серий 5503/5507. М.: Техносфера. 2017. ISBN 978-5-94836-332-5.

7.

Lodhi F.K., Hasan S., Hasan O., Awwad F. Low Power Soft Error Tolerant Macro

Synchronous Micro Asynchronous (MSMA) Pipeline // IEEE Computer Society An-

nual Sympos. on VLSI. Tampa. Florida. USA. 2014. P. 601-606.

8.

Iturbe X., Venu B., Ozer E., Das S. A Triple Core Lock-step (TCLS) ARM Cortex-

R5 Processor for Safety-Critical and Ultra-Reliable Applications // 46th Annual

IEEE/IFIP Int. Conf. on Dependable Syst. and Networks Workshop (DSN-W).

Lock-Step_TCLS_ARMR_CortexR-R5_Processor_for_Safety-Critical_and_

Ultra-Reliable_Applications.

9.

Gkiokas C., Schoeberl M.A. Fault-Tolerant Time-Predictable Processor // IEEE

Nordic Circuits and Syst. Conf. (NORCAS): NORCHIP and Int. Sympos. of

System-on-Chip (SoC). 2019. P. 1-6. 2019.

Fault-Tolerant_Time-Predictable_Processor.

10.

Mavis D., Eaton P. SEU and SET Modeling and Mitigation in Deep Submicron

Technologies // IEEE Int. Reliability Physics Sympos. April 15-19. 2007. Phoenix.

11.

Рождественский Ю.В., Степченков Ю.А., Дьяченко Ю.Г., Морозов Н.В.,

Степченков Д.Ю., Дьяченко Д.Ю. Метод повышения быстродействия самосин-

хронного умножителя // Проблемы разработки перспективных микро- и нано-

электронных систем. М.: ИППМ РАН. Вып. 1. 2020. С. 82-88. ISSN 2078-7707.

12.

Соколов И.A., Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В. По-

вышение сбоеустойчивости самосинхронных схем // Информатика и ее приме-

нения. 2020. Т. 14. № 4. С. 63-68.

131

13.

Stepchenkov Y.A., Kamenskih A.N., Diachenko Y.G., Rogdestvenski Y.V., Diachen-

ko D.Y. Improvement of the Natural Self-Timed Circuit Tolerance to Short-Term Soft

Errors // Advances in Sci., Technology and Engineering Syst. J. 2020. V. 5. No. 2.

14.

Emeliyanov V.V., Vatuev A.S., Useinov R.G. Impact of Heavy Ion Energy on Charge

Yield in Silicon Dioxide // IEEE Trans. on Nuclear Science. 2018. V. 65. No. 8.

15.

Dubrova E. Fault-Tolerant Design. KTH Royal Institute of Technology. Krista.

16.

Соколов И.А., Захаров В.Н., Степченков Ю.А., Дьяченко Ю.Г. Устрой-

ство сбоеустойчивого разряда самосинхронного регистра хранения. Пат. РФ

№ 2725778. Опубл. 06.07.2020. Бюл. № 19.

17.

Соколов И.А., Захаров В.Н., Степченков Ю.А., Дьяченко Ю.Г. Устрой-

ство сбоеустойчивого разряда самосинхронного регистра хранения. Пат. РФ

№ 2733263. Опубл. 01.10.2020. Бюл. № 28.

18.

Sokolov I., Stepchenkov Y., Diachenko Y., Rogdestvenski Y., Diachenko D. Increas-

ing Self-Timed Circuit Soft Error Tolerance // IEEE EastWest Design & Test Sym-

pos. (EWDTS). Varna. Bulgaria. 2020. P. 450-454.

19.

Makino H., Nakase Y., Suzuki H., Morinaka H., Shinohara H., Mashiko K. An 8.8

ns 54x54 Bit Multiplier with High Speed Redundant Binary Architecture // IEEE

J. of Solid-State Circuits. 1996. V. 31. No. 6. P. 773-783.

20.

Stepchenkov Y.A., Diachenko Y.G., Rogdestvenski Y.V., Diachenko D.Yu., Shiku-

nov Y.I. Self-Timed Multiply-Add-Subtract Unit Alternates // IEEE Conf. of Rus-

sian Young Researchers in Electrical and Electronic Engineering (EIConRus). 2020.

Статья представлена к публикации членом редколлегии А.М. Красносельским.

Поступила в редакцию 02.08.2021

После доработки 18.09.2021

Принята к публикации 15.10.2021

132