## НЕЙРОМОРФНЫЕ СИСТЕМЫ: ПРИБОРЫ, АРХИТЕКТУРА И АЛГОРИТМЫ

© 2023 г. К. А. Фетисенкова<sup>1, 2, \*</sup>, А. Е. Рогожин<sup>1, \*\*</sup>

<sup>1</sup>Физико-технологический институт им. К.А. Валиева Российской академии наук,

Нахимовский проспект, 34, корп. 1, Москва, 117218 Россия

<sup>2</sup>Московский физико-технический институт (государственный университет),

Институтский переулок, 9, Долгопрудный, 141701 Россия

\*E-mail: fetisenkova@ftian.ru

\*\*E-mail: rogozhin@ftian.ru

Поступила в редакцию 14.04.2023 г.

После доработки 10.07.2023 г.

Принята к публикации 10.07.2023 г.

Применение структуры и принципов работы человеческого мозга открывает большие возможности для создания искусственных систем на основе кремниевой технологии. Энергоэффективность и производительность биоподобной архитектуры могут оказаться существенно выше по сравнению с традиционной архитектурой фон Неймана. В данной работе представлен обзор наиболее перспективных архитектур ANN, SNN для биоподобных систем, называемых нейроморфными системами. Рассматриваются приборы для биоподобных систем, такие как мемристоры и сегнетоэлектрические транзисторы, для использования в качестве искусственных синапсов, определяющих возможность создания различных архитектур нейроморфных систем; методы и правила обучения структур для корректной работы при имитации биологических правил обучения, таких как долговременная синаптическая пластиичность. Обсуждаются проблемы, препятствующие реализации биоподобных систем, а также примеры архитектур, практически реализованных в настоящее время.

**Ключевые слова:** нейроморфная система, синапс, обучение, STDP, мемристор, архитектура, SNN, ANN, синаптическая пластиичность

**DOI:** 10.31857/S0544126923700461, **EDN:** SPOUJB

### 1. ВВЕДЕНИЕ

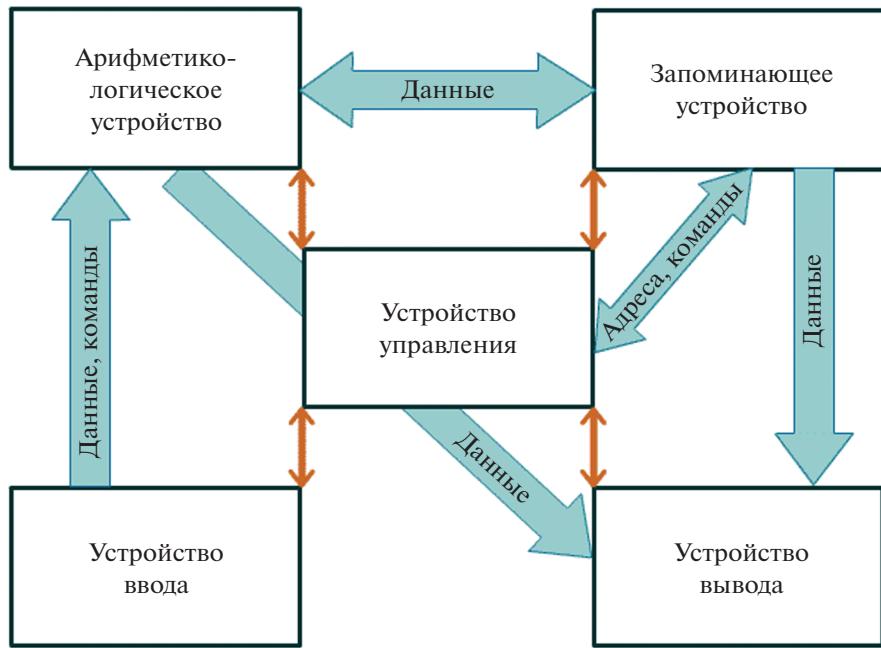

Проблема классической архитектуры фон Неймана, на которой основаны современные компьютеры состоит в том, что функции вычисления и хранения информации выполняются в разных областях интегральной схемы. Единое управление осуществляется в центральном процессоре, а область, в которой хранятся инструкции и данные, представляет собой блок низкоуровневой памяти. При выполнении инструкций центральным процессором, они должны быть переданы в него из памяти [1]. Команды передают информацию о месте хранения информации конкретных в данном случае операций, что также приводит к обращению в блок памяти. После выполнения полученных команд данные записываются в блок памяти (рис. 1) [2]. Таким образом, центральный процессор и память разделены между собой и для работы системы должны постоянно обмениваться данными. Это приводит к высокому энергопотреблению и снижению производительности всей системы.

Одной из перспективных альтернатив является разработка архитектуры нейроморфных систем, строение которых принципиально отличается от архитектуры фон Неймана и основывается на имитации работы нервной системы биологической структуры мозга. В такой архитектуре одни элементы системы используются как для записи и хранения информации, так и для ее изменения путем различных операций и вычислений. Они позволяют реализовать работу алгоритмов нейронных сетей с максимальной эффективностью.

С другой стороны, нейросетевые алгоритмы и усовершенствование их работы принципиально важно для развития многих областей. Большинство алгоритмов нейронных сетей сейчас реализованы на классической архитектуре фон Неймана [3]. В них имитируются биологические функции мозга, но преимущества живой нервной системы, например, меньшее энергопотребление и возможность быстрого действия или анализа окружающей среды, не достигаются. Масштабируемость и сверхнизкое энергопотребление также являются ключевыми преимуществами нейроморфных си-

Рис. 1. Схема вычислительной машины фон Неймана [2].

стем. Разработка нейроморфных систем может привести к стремительному развитию систем искусственного интеллекта [4].

## 2. НЕЙРОМОРФНЫЕ ВЫЧИСЛЕНИЯ

Термин “нейроморфный” был введен Кейвэром Мидом в 1990 г. и первоначально означал аналоговые схемы, ориентированные на эмуляцию поведения нейронных систем [5, 6]. Сегодня этот термин охватывает различные вычислительные системы, в которых принципы организации и рабочие механизмы имитируют биологическую деятельность мозга. Архитектуру нейроморфной системы отличает то, что для ее работы и последующего использования необходимо произвести обучение системы. Обучение связано с понятием синаптической пластичности, то есть способности системы менять коэффициент связи между нейронами. Для простейшего представления аналогий с биологическими системами коэффициент называется синаптический вес. Основная задача синапса в искусственной системе хранить значение синаптического веса, менять это значение в зависимости от сигналов, приходящих от нейронов или альтернативных правил обучения, а также участвовать в обработке проходящих сигналов.

Алгоритмы обучения системы, используемые материалы, элементы и технологии переключения, а также различные варианты устройства архитектуры являются основными направлениями разработки и исследования в области нейроморфных систем.

### 2.1. Алгоритмы для работы нейроморфных систем

Обучение нейроморфных систем основано на алгоритмах, определяющих правила изменения синаптического веса для каждого синапса, основного функционального элемента нейроморфной системы.

Существует большое количество правил обучения, предполагающих программное обучение, обучение на основе имитации биологических правил и подходы гибридного обучения, объединяющие в себе особенности двух первых подходов. Подробно эти правила будут рассмотрены в последующих разделах.

#### 2.1.1. Программный подход

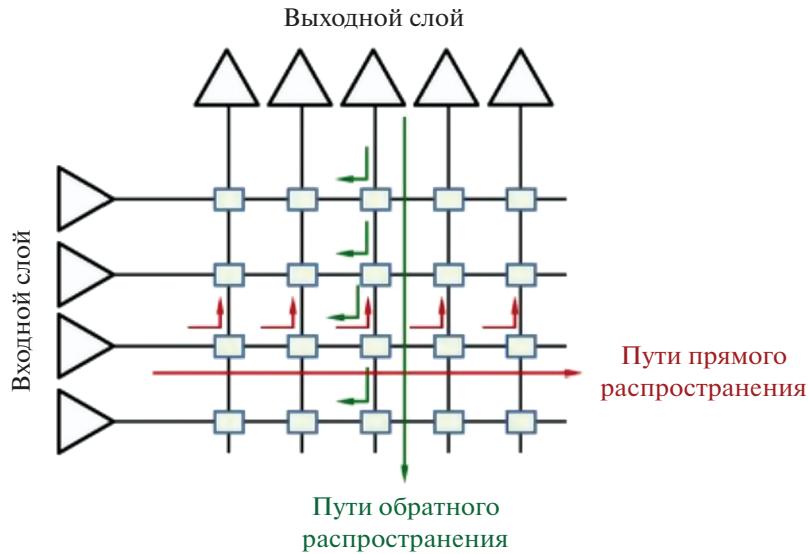

Программный подход предполагает использование алгоритма обратного распространения ошибки. Этот подход выполняется путем минимизации ошибки вычислений методом градиентного спуска. При этом расчеты для обновления весов проводятся вне архитектуры нейроморфной системы. Операция перезаписи значений синаптических весов выполняется в кросбаре при подключении периферийных транзисторов к синапсам. Для правильной работы алгоритма данная операция должна быть возможна как при прямом, так и при обратном распространении в структуре кроссбара (рис. 2) [7].

Поскольку алгоритм развивался на основе систем с архитектурой фон Неймана, предполагается, что синаптические веса всей сети, значения

Рис. 2. Маршруты доступа к синаптическим весам при прямом и обратном распространении [7].

функции активации нейронов и их производные всегда доступны в памяти. Это создает проблемы при адаптации к архитектуре нейроморфных систем. В основном это проблемы вычисления производных и аппаратной реализации доступа к синаптическим весам и их изменение.

### 2.1.2. Применение биологических правил обучения

Алгоритмы обучения, построенные на основе биологических аналогий, в перспективе могут позволить максимально использовать потенциал нейроморфных систем. Распространенные подходы биологического обучения – это правила синаптического обучения, основанные на алгоритме обучения STDP (синаптическая пластиность, зависящая от времени импульса) или БКМ (Бьяненсток–Купер–Монро), варьируемой частоте импульсов [8, 9]. В этих подходах обучение системы происходит с помощью серий импульсов различной формы, длительности и частоты [10].

Для реализации большинства алгоритмов при обучении необходимо иметь возможность обновлять синаптический вес произвольным образом. Для каждой ячейки синаптического веса требуется отдельная строка слов или битовая строка для произвольного доступа, что приводит к существенному усложнению схемы.

### 2.1.3. Гибридный подход

При гибридном подходе система обучается при помощи стандартных алгоритмов, например, обратного распространения ошибки. Затем параметры нейросети записываются в эквивалентную спайковую нейроморфную систему SNN. Для рабо-

ты системы такого типа обучения нейросеть должна быть оснащена механизмом для записи предварительно полученных значений синаптических весов. Для этого необходим доступ и способ для программирования значений синаптического веса.

Недостатки подхода связаны со снижением точности из-за преобразования системы [11, 12]. Также проблемой при использовании такого подхода является дрейф проводимости, приводящий к неконтролируемому изменению значений синапсов.

## 2.2. Логические вычисления

Одной из необходимых составляющих корректной работы нейроморфных систем является способность производить вычисления в той же области интегральной схемы, где уже хранятся данные, без их перемещения между блоками памяти и управляющими и арифметическими модулями. Например, нейроморфные системы возможно использовать для аналогового векторно-матричного умножения и цифровой логики.

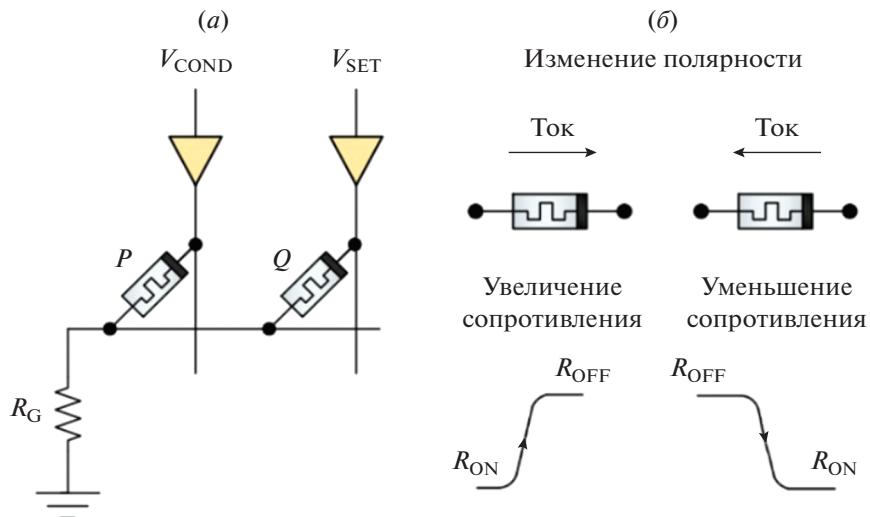

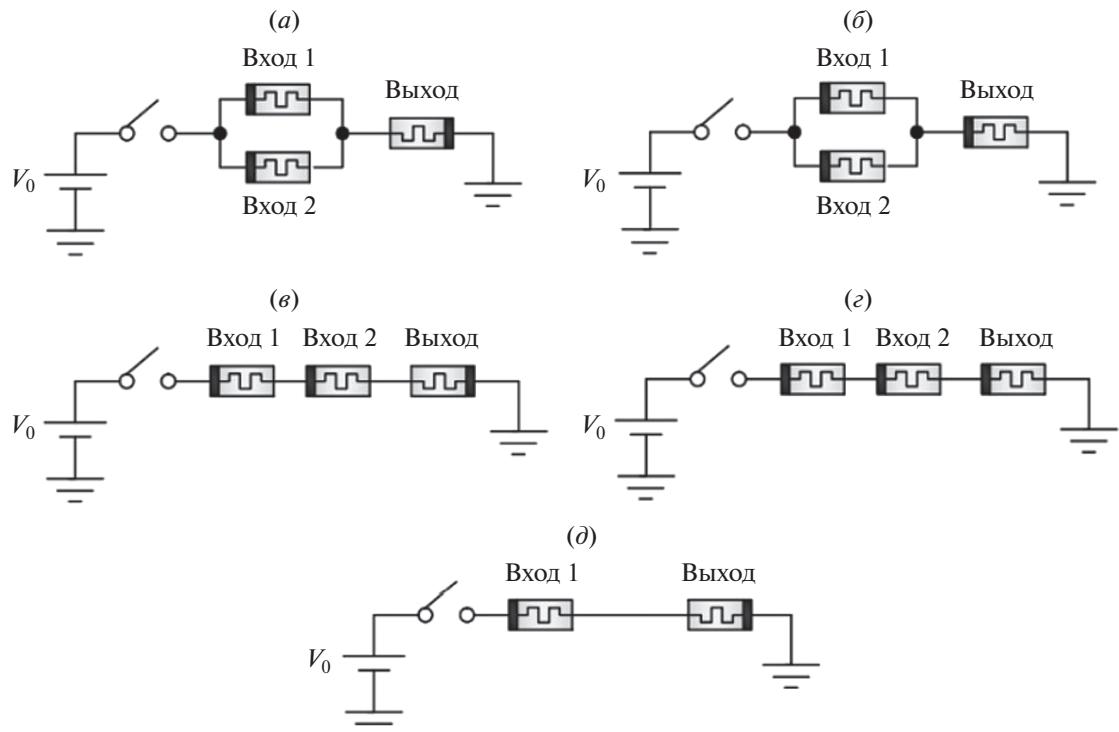

Одной из логических операций, легко реализуемых в нейроморфных системах, является материальная импликация ( $p \rightarrow q$  или  $p \text{ IMP } q$ ) [13]. Важной особенностью этой функции является то, что наряду с операцией FALSE (которая всегда дает логическое значение “0”), она составляет полный вычислительный базис, который может быть использован для сборки любой логической операции. Эту функцию можно реализовать на основе двух мемристоров с помощью схемы, показанной на рис. 3 [13].

Логическими переменными являются сопротивления  $P$  и  $Q$ , так что логический уровень “1” соответствует состоянию низкого сопротивления

Рис. 3. (a) Схема для реализации мемристивной материальной импликации; (б) условное обозначение полярности для увеличения/уменьшения сопротивления [13].

Рис. 4. Логические элементы MAGIC: (a) NOR, (б) OR, (в) NAND, (г) AND и (д) NOT [13].

$R_{ON}$ , а уровень “0” соответствует значению высокого сопротивления  $R_{OFF}$ . Ввод значений выполняется путем приложения напряжений  $V_{COND}$  и  $V_{SET}$  к  $P$  и  $Q$ , соответственно. Состояния мемристоров переключаются под действием напряжения и благодаря простой структуре легко встраиваются в кроссбар структуру. Такая энергонезависимая двоичная логика называется логикой с сохранением состояния и может быть реализована не только с помо-

щью схем, содержащих управляемые источники напряжения [14, 15], но и с помощью схем, основанных только на мемристорах [16, 17].

В таком подходе, названном MAGIC, логический элемент строится с мемристором на каждом входе и дополнительным мемристором на выходе (рис. 4) [13]. Как и в обычной цифровой схеме, логические значения соответствуют значениям проводимости элементов.

Рис. 5. Строение биологического нейрона [18].

MAGIC и импликационная логика могут быть интегрированы в массив кроссбаров и позволяют выполнять вычисления в памяти, то есть одновременную обработку и хранение данных элементами схемы.

### 3. НЕЙРОМОРФНЫЕ СИСТЕМЫ

#### 3.1. Строение биологической системы

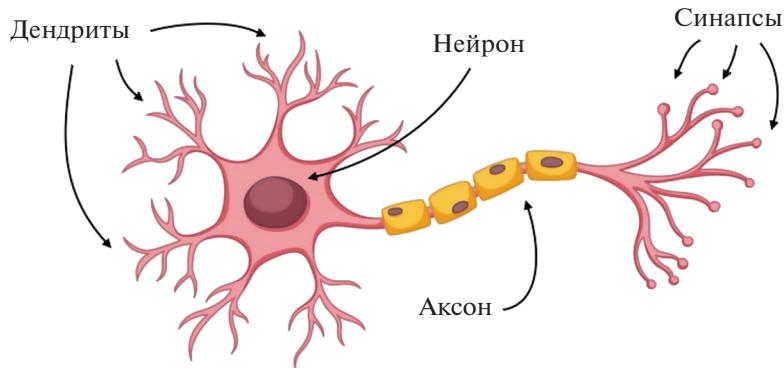

Нервная система, как и другие системы организма, состоит из клеток. Эти клетки называют нейронами. Для связи нейронов друг с другом и образования нейронной сети существуют специальные контакты – синапсы. Типичный нейрон состоит из тела, дендритов и аксона (рис. 5) [18]. По дендритам и аксону сигналы передаются между нейронами.

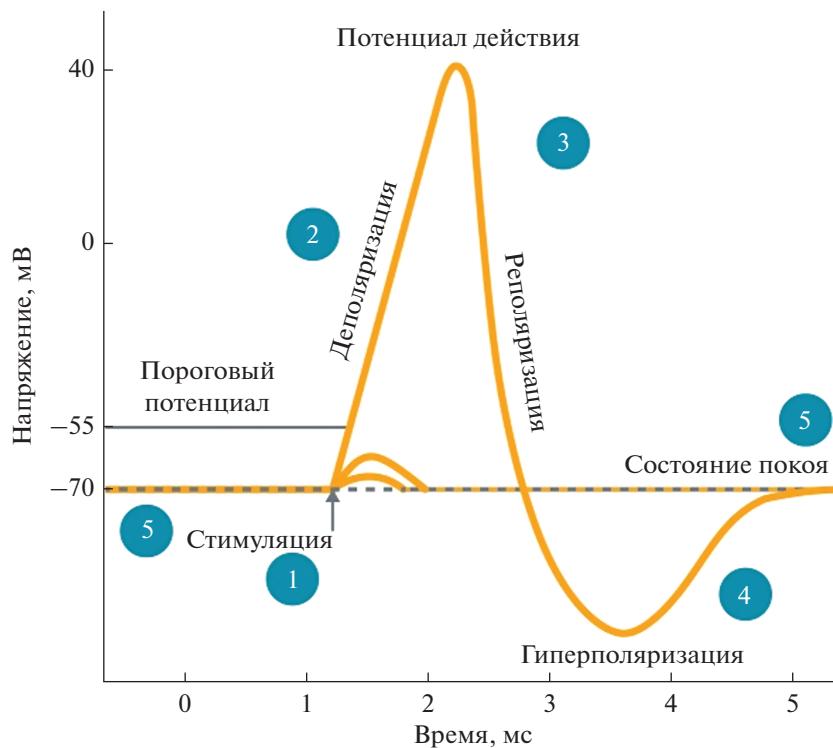

Для адаптивной работы биологической нейронной сети, нейрон собирает сигналы [19], то есть импульсы, приходящие к нему по дендритам, и затем передает свой сигнал по аксону другому нейрону или клетке. В биологической сети такой импульс генерируется благодаря деполяризации клетки в ходе химических и биологических реакций (рис. 6) [20].

Сигнал от нейрона к нейрону передается за счет образования специальных соединений между нейронами – синапсов. Синапсы оказывают влияние на то, какой интенсивности будет сигнал и на скорость его передачи между нейронами. Синапс определяет силу связи между нейронами.

В настоящее время известно, что информационные функции мозга определяются не свойствами конкретных клеток, а свойством пластичности передачи импульсного сигнала между клетками. Синаптическая пластичность или изменение функциональных свойств нервных клеток при обучении проявляется в усилении (потенциация (LTP)) или ослаблении (депрессия (LTD)) эффективности синаптических контактов [21].

Синаптическая пластичность зависит от последовательности, частоты и амплитуды приходящих на нейрон импульсов. Обучение в случае биологической нейронной сети определяется количеством нейромедиаторов (клетки влияющие на скорость передачи сигнала) образующихся в пре-синаптической области нейрона, скоростью высвобождения и удаления ионов в синаптической щели, а также другими биологическими и химическими реакциями [20]. Таким образом, пути распространения импульсов в биологической нейронной сети способны меняться благодаря свойству синаптической пластичности.

#### 3.2. Искусственная нейронная сеть

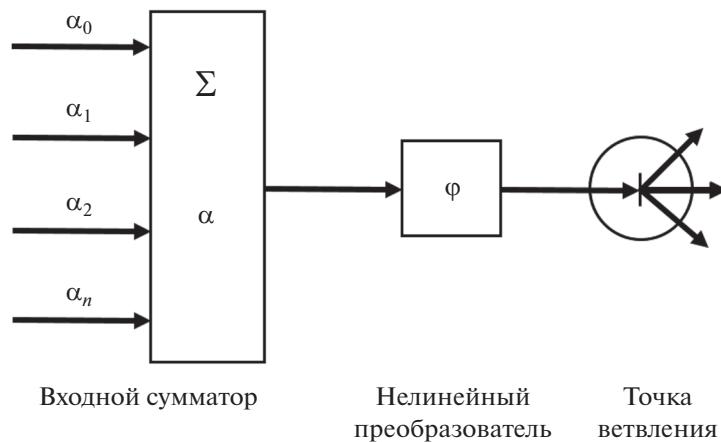

Искусственная нейронная сеть представлена различными алгоритмами для решения задач, например, классификации или машинного обучения. Принцип работы алгоритмов аналогичен работе биологических нейронных сетей. Нейроном здесь выступает элемент, в котором суммируются все приходящие в него сигналы, и после применения к полученному значению функции активации, на выход выдается один сигнал (рис. 7).

Синапсы в искусственной нейронной сети определяются специальными переменными весов, которые отражают важность каждой конкретной связи между нейронами. Эти переменные называют синаптическими весами:

$$x \xrightarrow{\alpha} \alpha x. \quad (1)$$

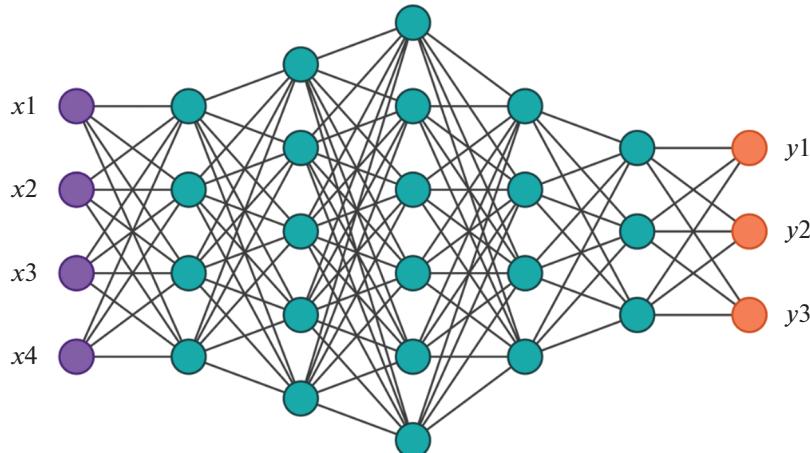

Простейшая нейронная сеть (рис. 8) состоит из входного слоя, нескольких скрытых слоев и выходного слоя [23].

Первый слой нейронов принимает входные значения сигналов. Каждое входное значение умножается на коэффициент синаптического веса, отражающего связь между нейронами разных слоев. В каждом нейроне скрытого слоя эти значения суммируются и нормируются с помощью функции активации. В результате сравнения значений, полу-

Рис. 6. Фазы сигнала в биологическом нейроне [20].

Рис. 7. Схематическое представление нейрона искусственной нейронной сети.

ченных после вычислений скрытого слоя, определяются нейроны важные для решения поставленной задачи. Эта операция проводится на каждом уровне. На выходном слое обученная нейронная сеть выдает решение задачи, которое соответствует нейрону с максимальным значением. Например, в задачах классификации или распознавания образов выходной слой нейронов соответствует заранее известным вариантам ответа, а обученная нейронная сеть выбирает один из них как решение.

### 3.3. Различные возможные элементы нейроморфных систем

#### 3.3.1. Мемристоры

Мемристор представляет собой устройство, сопротивление которого можно изменять путем подачи напряжения [24].

Мемристоры обычно классифицируют по механизму переключения. Основные параметры мемристоров – время переключения, диапазон

Рис. 8. Упрощенная схема строения нейронной сети [23].

изменения сопротивлений, энергия переключения, надежность [25]. Существуют четыре типа механизмов переключения: механизм электрохимической металлизации (ECM) [26], механизм изменения валентности (VCM) [27], термохимический механизм (TCM) [28], и механизм изменения фазы (PCM) [29, 30]. Мемристоры с иными механизмами переключения, например, на основе перехода Мотта [31], с фотонно-индуцированным переключением [32] или сегнетоэлектрическим переходом [33], также исследуются в качестве устройств для биоподобных вычислительных систем.

Кроме того, в различных структурах мемристоров при резистивном переключении [34, 35] наблюдается непрерывное изменение сопротивления от HRS к LRS, и поэтому у устройства может быть больше двух устойчивых состояний с различными значениями сопротивлений, что очень удобно для использования таких мемристоров в аналоговых приборах и нейроморфных вычислительных системах.

Мемристоры могут использоваться в цифровых и аналоговых схемах. Примерами цифрового применения мемристоров можно назвать импликационную логику [36] и логику NAND [37].

Одним из наиболее перспективных направлений для применения мемристоров являются схемы памяти на основе мемристивных устройств (ReRAM). Малый размер мемристора может обеспечить высокую плотность хранения. Для этих устройств характерны энергонезависимость и малое время переключения [38].

Возможность создания аналоговых систем на основе мемристоров вызывает большой интерес и открывает новые перспективы для их применения в микроэлектронике. Мемристоры со ступенчато или непрерывно меняющимся сопротивлением могут использоваться в самых различных аналоговых схемах. Их можно использовать в схемах компараторов напряжения, неинвертирую-

щих усилителей и триггера Шмитта, а также в генераторах, например, генераторах с частотным мостом Вина или с фазовращателем, в фильтре нижних частот первого порядка с настраиваемой частотой, полосовом фильтре второго порядка с настраиваемым коэффициентом добротности, в делителях мощности, антенах и других [13].

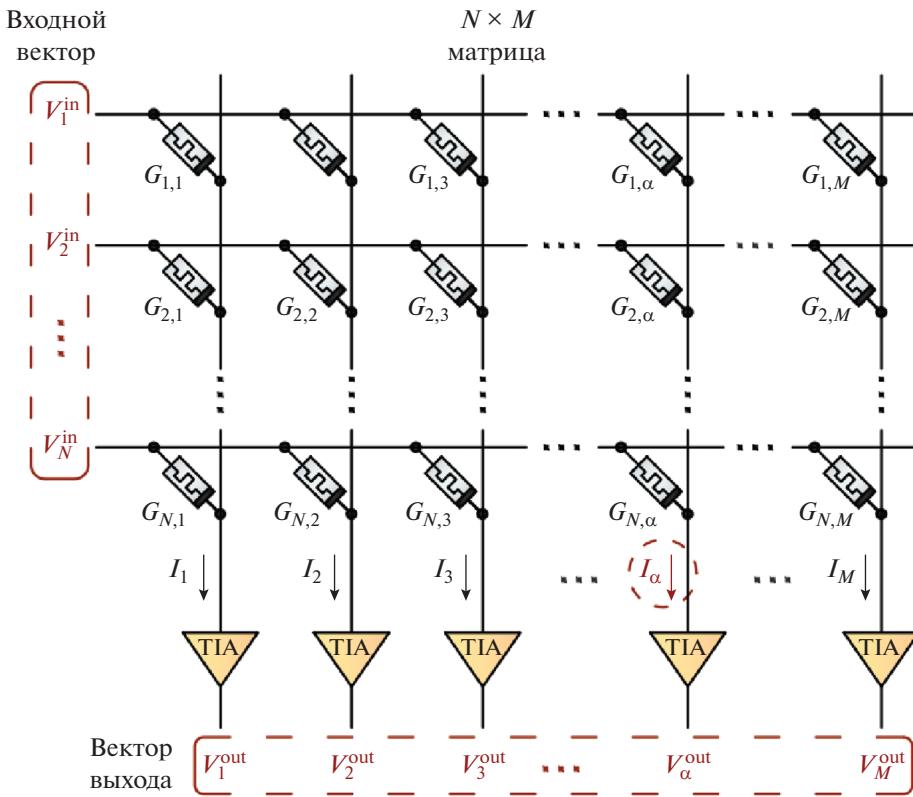

В схемах на основе мемристоров возможно выполнение полного набора арифметических операций (сложение, вычитание, умножение, деление), а также более сложных задач, таких как параллельная факторизация и дробное деление [39]. В мемристорных аналоговых схемах можно осуществить операции векторно-матричное умножения на основе закона Ома и суммирования на основе закона Кирхгофа. Эта задача может быть выполнена за один шаг с помощью мемристорного массива кроссбаров (рис. 9) [40]. Для произвольного столбца  $\alpha$  ток задается формулой [13]:

$$I_\alpha = \sum_{k=1}^N V_k^{\text{in}} G_{k,\alpha}, \quad (2)$$

где  $V_k$  – входной вектор напряжения, а  $G_{k,\alpha}$  – вектор проводимости для столбца  $\alpha$ . Выходные токи могут быть преобразованы в напряжения, например, с помощью трансипедансных усилителей (TIA). Этот подход может быть использован для выполнения нейроморфных вычислений.

Существуют другие подходы к реализации нейроморфных систем. Для работы нейроморфных сопроцессоров на основе CMOS требуется специальное программное обеспечение, информация о весах хранится в памяти. Такие системы гарантируют высокую надежность нейроморфных вычислений, однако, для них характерна низкая эффективность. Для обеспечения конкурентоспособности нейроморфных систем на основе мемристоров должны быть обеспечены уникальные характеристики мемристоров.

Рис. 9. Кросбар-массив мемристоров для векторно-матричного умножения (VMM) [13].

### 3.3.2. Сигнетоэлектрические транзисторы

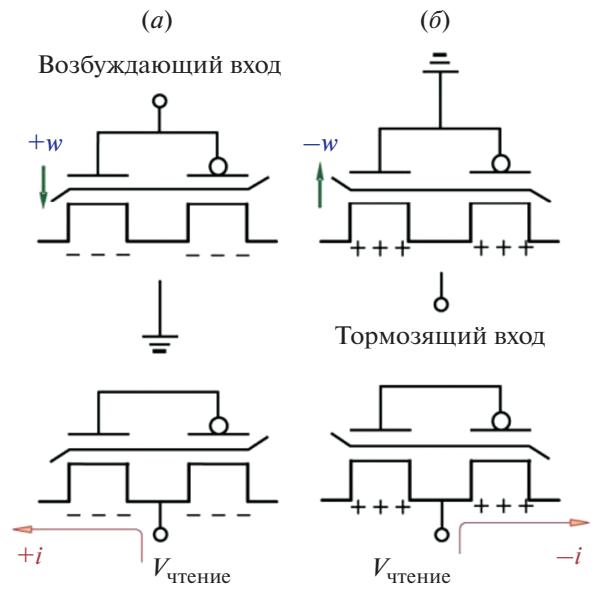

Возможным вариантом реализации синапса в нейроморфной системе является использование сигнетоэлектрических транзисторов (рис. 10) [7]. В сигнетоэлектриках благодаря доменной структуре и способности к спонтанной поляризации возможно контролируемое изменение объемного значения поляризации. Поляризация сигнетоэлектриков меняется в электрическом поле. Важным преимуществом сигнетоэлектрических транзисторов является возможность создания возбуждающего и тормозящего синапса в простой ячейке из двух транзисторов р и н типа [41].

При этом изменение поляризации, приводящее к увеличению положительных значений синаптического веса, соответствуют возбуждающему постсинаптическому потенциалу, а изменение поляризации, приводящее к увеличению отрицательных значений синаптического веса – тормозящему постсинаптическому потенциалу. Таким образом состояние сигнетоэлектрического синапса меняется в зависимости от поданного импульса напряжения, имитируя простейшие биологические функции обучения. Значения синоптического веса сигнетоэлектрического прибора могут изменяться в большем диапазоне.

Проблемы сигнетоэлектрических транзисторов связаны с тем, что значения проводимости изменя-

ются не линейно. Это ограничивает возможности аналогового применения. Также для сигнетоэлектрических приборов характерна низкая надежность системы. Эта проблема может быть решена

Рис. 10. Реализация возбуждающего (a) и тормозящего (b) синапса на основе сигнетоэлектрических транзисторов. Знак синаптического веса определяется направлением тока [7].

Рис. 11. Кроссбар-массив сегнетоэлектрических конденсаторов для векторно-матричного умножения (VMM) [7].

с помощью дополнительных слоев в затворной структуре транзисторов [42].

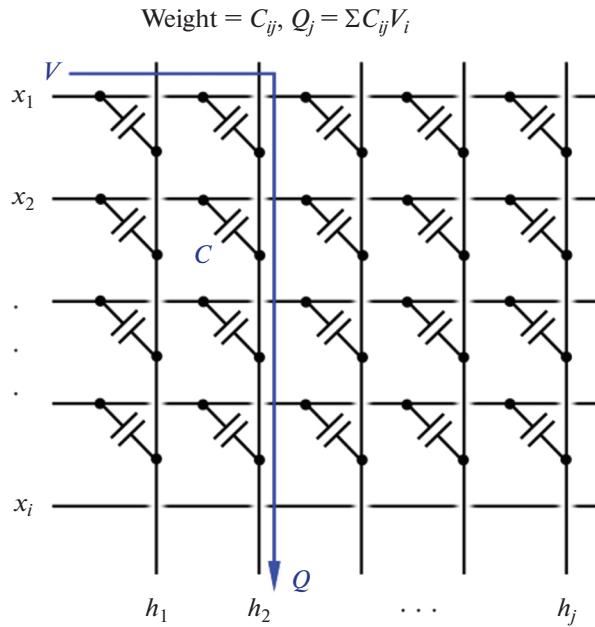

Сегнетоэлектрические конденсаторы также применяют для нейроморфных приложений. В структуре кроссбара сегнетоэлектрических конденсаторов реализуют векторно-матричное умножение (рис. 11).

В отличие от структуры кроссбара мемристоров, где вычисления производятся благодаря изменению проводимости, в схеме из сегнетоэлектрических конденсаторов используется изменение емкости:

$$Q_j = \sum_{i=1}^n V_i^{\text{in}} C_{i,j}. \quad (3)$$

#### 4. АППАРАТНОЕ ОБЕСПЕЧЕНИЕ НЕЙРОМОРФНЫХ СИСТЕМ НА ОСНОВЕ МЕМРИСТОРОВ

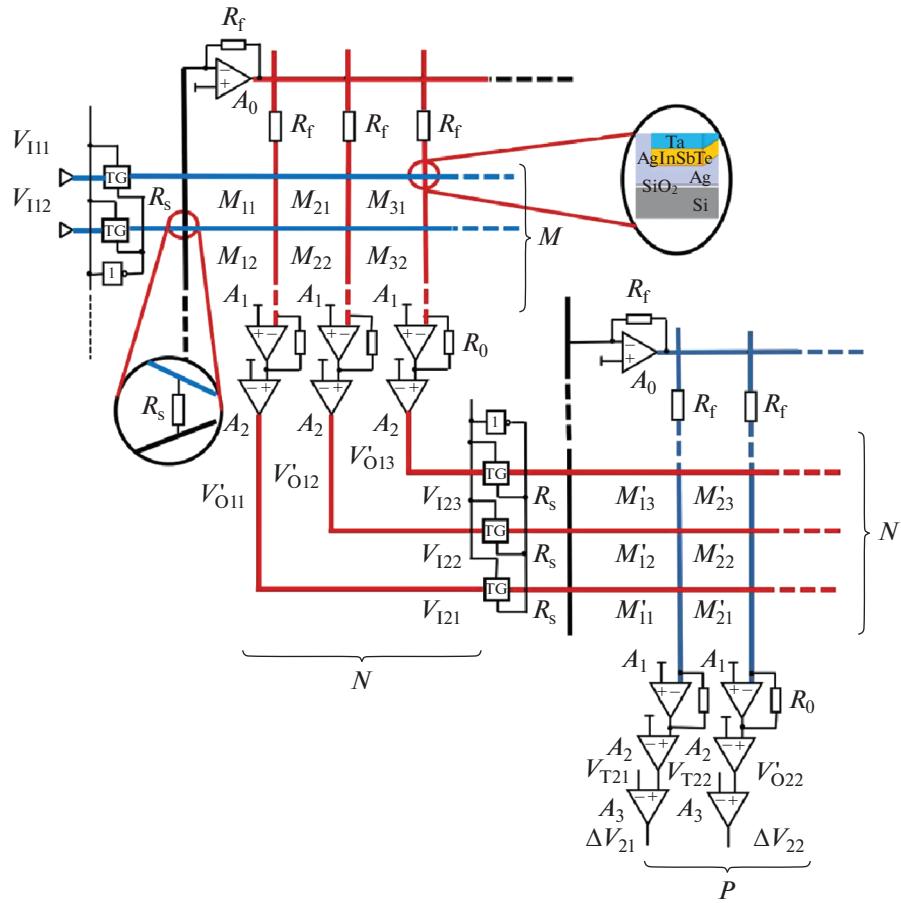

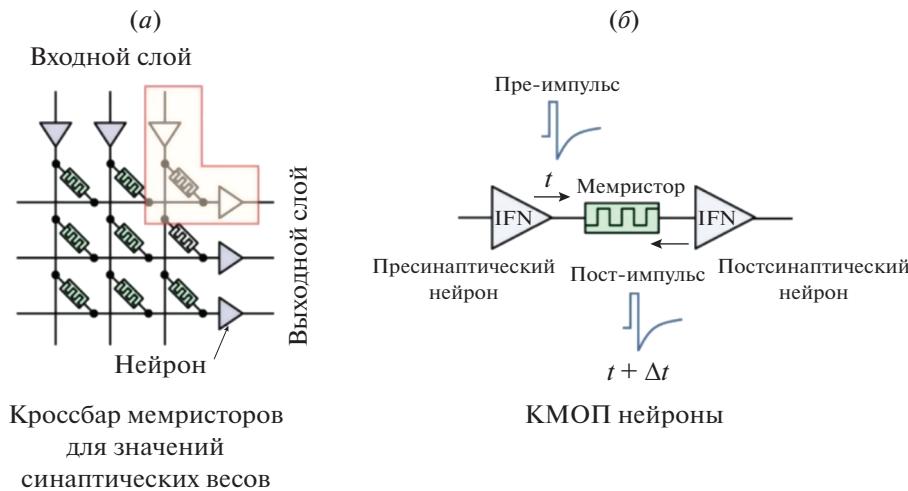

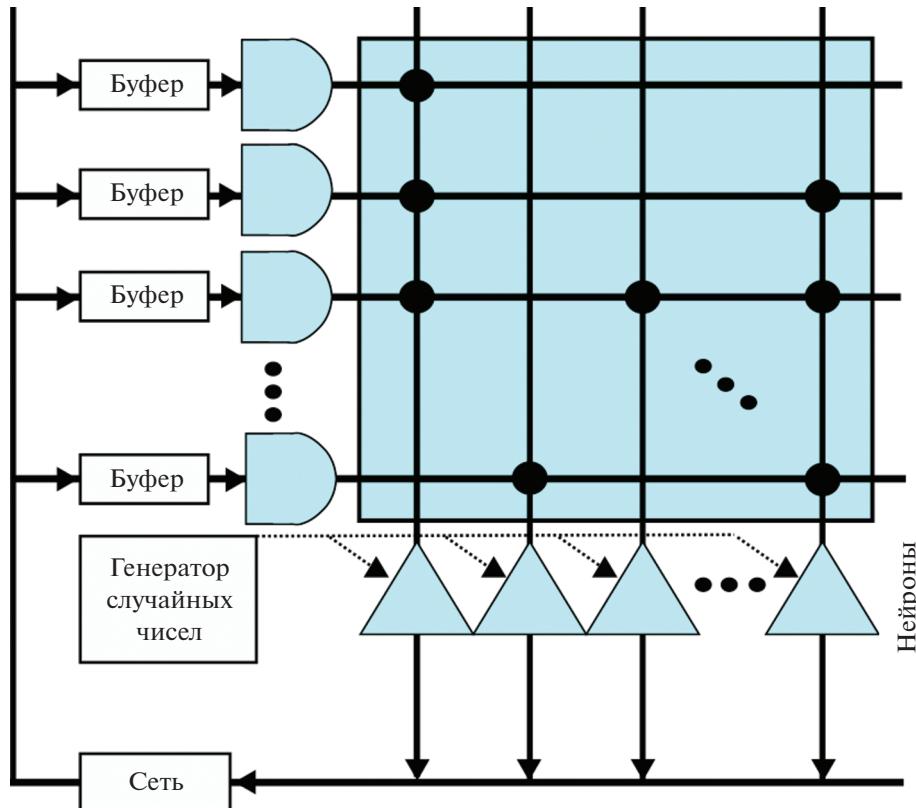

Типичное аппаратное обеспечение для нейроморфных систем состоит в основном из кроссбаров мемристоров, нейронов и периферийных схем. В такой структуре вертикальные и горизонтальные линии (рис. 12) играют роль нейронов на разных

Рис. 12. Схема нейроморфной системы ANN с кроссбарами мемристоров [44].

Рис. 13. (а) кроссбар SNN с мемристорными синапсами, соединяющими нейроны; (б) возбуждение матричного синапса до и после импульсов, разделенных интервалом  $\Delta t$  [7].

уровнях. В точке пересечения каждый нейрон предыдущего слоя связывается с нейроном последующего слоя при помощи мемристоров, выполняющих функцию синапсов. Связь между нейронами определяется проводимостью мемристоров.

Способ обучения нейроморфной системы – алгоритм, определяющий правила изменения сопротивления каждого мемристорного синапса в архитектуре нейроморфной системы. Виды архитектур нейроморфных систем и роль мемристорного устройства в них рассматриваются в следующих разделах.

#### 4.1. Нейроморфные системы для ANN (Artificial neural network)

Традиционным вариантом обучения для алгоритмов нейронных сетей является математический алгоритм обратного распространения ошибки. Таким образом при адаптации нейроморфных архитектур для нейронных сетей метод обратного распространения ошибки сохраняется [43]. При таком обучении новые значения рассчитываются для каждого устройства методом градиентного спуска. После пересчета значения весов перезаписываются (рис. 12) [44].

В системе кроссбаров нейроморфной системы хранятся значения синаптических весов разных слоев в соответствии с алгоритмом нейронной сети. Кроссбар мемристоров определяет процессы обучения и работы нейроморфной системы для ANN.

Для функционирования ANN нейроморфных систем необходимы периферийные схемы. Они используются для управления процессом чтения/записи в кроссбара, а также выполняют сопутствующие расчеты для задачи оптимизации. Например, задачу расчета значений производных

градиентного спуска при обучении с помощью обратного распространения ошибки.

#### 4.2. Импульсные нейроморфные системы (SNN)

Альтернативный вариант – обучение имитирующее биологическое правило обучения STDP [45], при котором значение сопротивления мемристора меняется при подаче серий импульсов напряжения согласно правилам долговременного и коротковременного обучения. Нейроморфные системы, для обучения которых применяются правила STDP, называются импульсными нейроморфными системами (SNN).

Импульсные нейроморфные системы обычно также основаны на кроссбар-конфигурации, как показано на рис. 13 [7]. Импульсные нейроморфные системы (SNN) могут быть обучены выполнению нескольких задач с использованием набора различных правил/алгоритмов обучения [46].

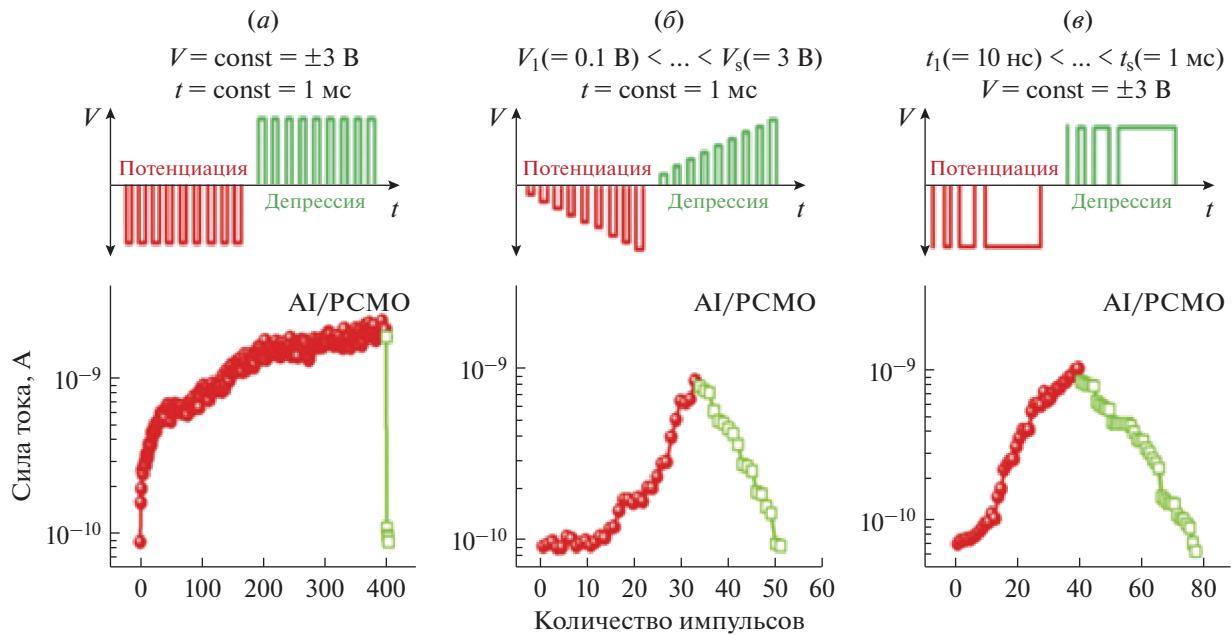

Импульсы, подаваемые на нейроны, в зависимости от частоты, амплитуды и сдвига фазы могут изменить значение веса синапса в большую или меньшую сторону. Способность элемента менять значение синаптического веса в ответ на сигналы системы называется синаптической пластичностью [47]. Правила обучения описывают механизм синаптической пластичности [48]. По аналогии с биологическими правилами в структуре кроссбара мемристоров реализуется долговременная пластичность, включающая долговременные потенциацию (LTP) и депрессию (LTD), заключающиеся в увеличении и уменьшении значения проводимости, в зависимости от параметров поданных серий импульсов.

Для корректной работы таких структур очень важны линейность и симметричность обновле-

Рис. 14. (a) Долговременная пластиность. Линейность и симметричность LTP/LTD при одинаковых импульсах, (b) при импульсах с возрастающим значением амплитуды и (c) ширины импульса [49].

ния значений LTP/LTD. При подаче серий импульсов с возрастающим значением амплитуды или ширины импульса можно добиться серьезного улучшения как для линейности, так и для симметрии пластиности (рис. 14) [49]. Однако методы осуществления такой подачи серий импульсов не совместимы со схемой кроссбара, в которой весь массив синаптических весов обновляется одновременно.

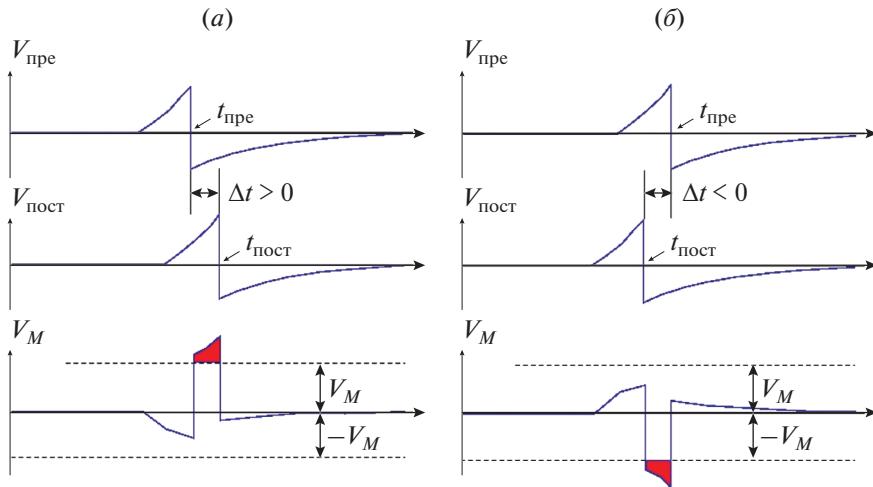

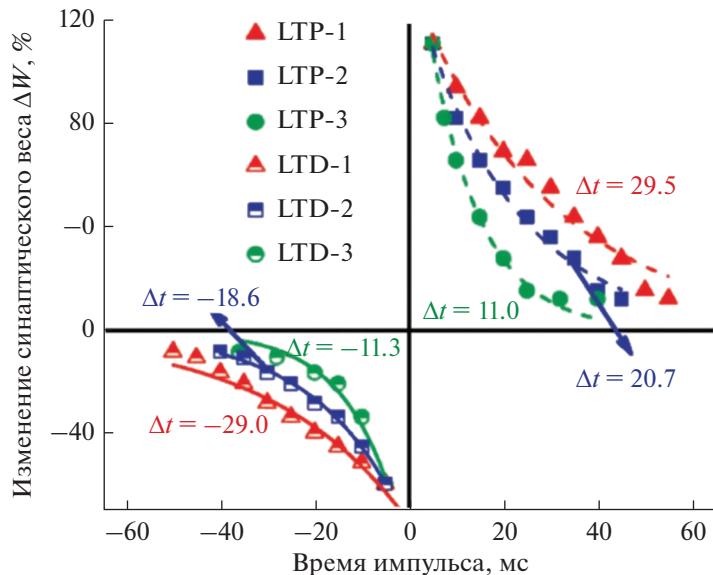

Самым распространенным правилом обучения для SNN представляется биоподобная синаптическая пластиность, зависящая от времени импульса (STDP). При типичном правиле STDP синаптический вес подвергается долговременной потенциации LTP (увеличение значения проводимости) или долговременной депрессии LTD (уменьшение значения проводимости), если временная задержка между “пресинаптическим” и “постсинаптическим” импульсами  $\Delta t > 0$  и если  $\Delta t < 0$ , соответственно. “Пресинаптическими” и “постсинаптическими” здесь называются импульсы с прямым и обратным распространением, соответственно. В кроссбар структуре форма импульса в серии выбирается таким образом, чтобы учесть временную задержку  $\Delta t$  для реализации потенциации и депрессии (рис. 15) [50].

Основной метод реализации STDP для кроссбара мемристорных устройств состоит в том, что на каждый синапс приходят импульсы от нейронов в независимой друг от друга последовательности. Амплитуды пре- и постсинаптических импульсов накладываются друг на друга. Такой результирующий импульс напряжения изменяет проводимость

устройства в соответствии с правилом обучения. На рис. 16 [50] показан график зависимости изменения значения проводимости мемристора от  $\Delta t$ .

## 5. ПРИМЕРЫ РЕАЛИЗАЦИИ АРХИТЕКТУР НЕЙРОМОРФНЫХ СИСТЕМ

Разработка архитектур нейроморфных систем перспективна и привлекает большое внимание различных компаний и исследовательских центров. Чипы разрабатываются для повышения быстродействия, точности и снижения энергопотребления. Так как улучшение всех характеристик устройств одновременно обычно невозможно, критерии улучшения и оптимизации каждой характеристики при разработке чипа выбираются в зависимости от задач системы. При работе с машинным переводом текста или речи меньше возможностей для оптимизации системы, так как важна точность результата. С другой стороны, например для распознавания и классификации объектов на изображении можно пожертвовать некоторой точностью для упрощения системы. Примеры архитектур нейроморфных систем рассматриваются в последующих разделах.

### 5.1. Нейроморфная система Loihi

Нейроморфный исследовательский тестовый чип Loihi разработан Intel Labs. В чипе используется асинхронная нейронная сеть (SNN) для реализации адаптивных параллельных вычислений, используемых для реализации обучения с высокой

Рис. 15. Форма импульса, учитывающая временную задержку “пресинаптическим” и “постсинаптическим” импульсами [50].

Рис. 16. Пример графика для искусственной реализации правила обучения STDP с помощью синаптических мемристорных устройств [50].

эффективностью. Чип представляет собой микросхему с 128 нейроморфными ядрами, изготовленную по 14-нм техпроцессу Intel и оснащенную уникальным программируемым механизмом обучения микрокодом для встроенной SNN [51, 52].

Благодаря асинхронной импульсной нейронной сети (SNN) Loihi чипы генерируют импульсы только в активированные нейроны. Нейроморфные ядра, содержащие множество нейронов, взаимосвязаны и получают импульсы из всех частей сети. Синапсы работают в соответствии с биологической имитацией. Таким образом, ядро запускает свои собственные импульсы в подключен-

ные нейроны только в случае активации от импульсов других ядер. В любой момент времени один или несколько активированных нейронов могут посыпать импульс соседним нейронам через синапсы. Условия и порог активации для каждого нейрона настраивается отдельно. Возбуждающие и тормозные синапсы работают согласно правилам долговременного обучения. Уникальной особенностью нейроморфных ядер Loihi является интегрированный механизм, обеспечивающий полное обучение на чипе с помощью программируемых правил обучения [53]. Обучение выполняется отдельным блоком для каждого ядра.

Таблица 1. Сравнение нейроморфных систем на основе чипа Loihi [51]

| № | Название        | Система               | Количество чипов, штук | Количество синапсов, $10^6$ | Количество нейронов, $10^3$ |

|---|-----------------|-----------------------|------------------------|-----------------------------|-----------------------------|

| 1 | Kapooh Bay      | USB FF                | 1–2                    | 130–260                     | 131–262                     |

| 2 | Wolf Mountain   | Плата                 | 4                      | 520                         | 524                         |

| 3 | Nahuku          | Плата расширения FPGA | 8–32                   | 1040–4160                   | 1 048–4200                  |

| 4 | Pohoiki Beach   | Многоплатная система  | 64                     | 8320                        | 8388                        |

| 5 | Pohoiki Springs | Многоплатная система  | 768                    | 99 840                      | 100 663                     |

В табл. 1 представлены системы на основе Loihi, которые масштабируются до большого количества нейронов и синапсов.

### 5.2. Нейроморфная система TrueNorth

Чип нейроморфного процессора TrueNorth, исследовательского проекта компании IBM изготовлен, по технологическому процессу Samsung 28 нм площадью 430  $\text{мм}^2$ . Архитектура построена по асинхронной технологии и реализует 1 млн нейронов в 4096 ядрах при энергопотреблении 70–100 мВт (рис. 17) [55]. Ядро имеет 256 входов (аксонов) и 256 выходов (нейронов). Архитектура обеспечивает связь между внутренними объектами ядра при помощи программируемого матричного коммутатора 256  $\times$  256 [54]. Связь между ядрами осуществляется при помощи маршрутизатора.

Вычисления и передача сигнала между ядрами в архитектуре производятся только для активированных нейронов и ненулевых значений для синаптических весов. Для каждого нейрона отдельно настраивается порог для активации и генерации импульса. Сигналы в отдельном ядре распределяются по нейронам с учетом синаптических весов. Синаптический вес кодируется 2 битами. Синапс может быть возбуждающим (с фиксированным для данного нейрона весом), тормозным (тоже – с одним и тем же весом для всех синапсов одного нейрона) или отсутствующим. Связь и вычисления связаны временной зависимостью. Синаптические связи имеют 4-битную временную задержку.

Для работы и обучения новой архитектуры разработана специальная среда Corelet Programming Environment. TrueNorth подходит для исполнения рекуррентных нейронных сетей, которые могут применяться для классификации различной информации, в том числе, изображений, речи и видео [54, 55].

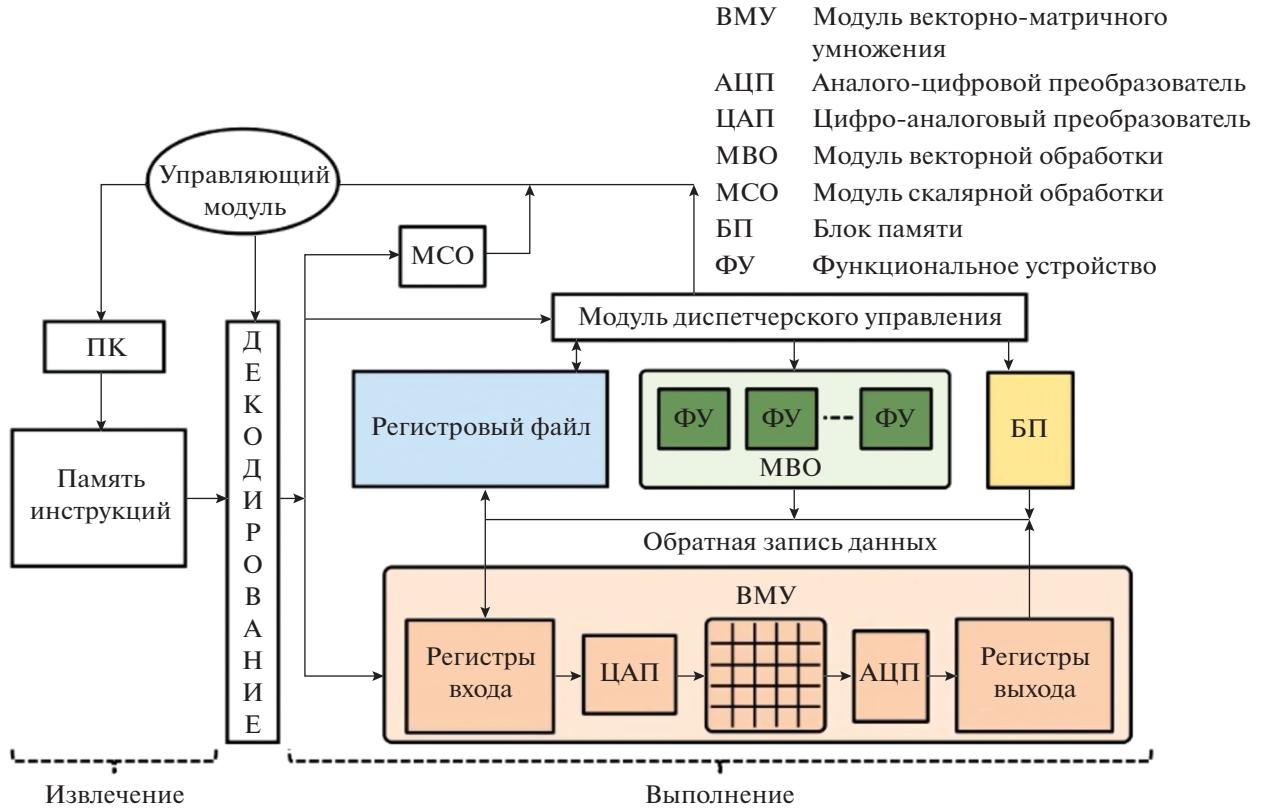

### 5.3. Нейроморфная система PUMA

PUMA является первым программируемым сверхэффективным ускорителем на основе ги-

бридной технологии объединяющей мемристоры и CMOS. Пространственная архитектура PUMA организована в три уровня: ядра, плитки и узлы. Ядра состоят из аналоговых кроссбаров, функциональных блоков и конвейера выполнения команд. Плитки состоят из нескольких ядер, соединенных через общую память. Узлы (модули) состоят из нескольких плиток, соединенных через встроенную сеть. Модуль PUMA площадью 90  $\text{мм}^2$  может хранить модели ML (машинного обучения) с объемом данных о весе до 69 МБ. Для выполнения крупномасштабных задач узлы могут быть соединены вместе с помощью межблочного соединения “чип к чипу”. Базовая и плиточная архитектуры обеспечивают программируемость и универсальность кроссбаров мемристоров без ущерба для их энергоэффективности и площади. Обзор базовой архитектуры показан на рис. 18 [56].

Ускоритель PUMA работает на частоте 1 ГГц и может достигать КПД и  $5.77 \times 10^{11}$  операций в секунду на 1  $\text{мм}^2$  площади и  $8.37 \times 10^{11}$  операций в секунду на 1 Ватт мощности. Оценка различных приложений ML, таких как распознавание изображений, машинный перевод и языковое моделирование (5–800 М синапсов), показывает увеличение значения энергоэффективности. PUMA достигает  $2.446 \times$ , а также меньшую временную задержку при выводе и перезаписи данных по сравнению с современными графическими процессорами. По сравнению с ускорителем на базе мемристора, используемым в конкретных приложениях, PUMA требует небольших затрат энергии при аналогичной задержке вывода и дополнительной программируемости [56].

Таким образом, базовая архитектура обеспечивает программируемость при сохранении эффективности структуры кроссбара. Использование блока SIMD (Single instruction, multiple data) [57], обеспечивающего параллелизм и многопоточность вычислений, для минимизации энергопотребления при перезаписи и встроенной в ПЗУ оперативной памяти позволяет выполнять линейные, нелинейные и трансцендентные векторные операции. Оптимизация перемещения данных обес-

Рис. 17. Архитектура ядра TrueNorth [54].

Рис. 18. Базовая архитектура PUMA [56].

Рис. 19. Пример маршрута тока утечки в кросбаре [59].

печивается за счет операндов перераспределения, повторно используемых в слоях входных данных, правильного размера файла регистра и гибких инструкций доступа к памяти.

## 6. ПРОБЛЕМЫ РЕАЛИЗАЦИИ АРХИТЕКТУР НЕЙРОМОРФНЫХ СИСТЕМ

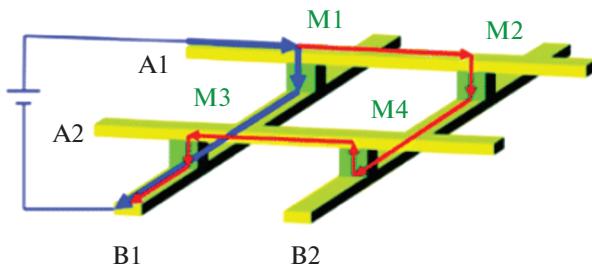

Основные проблемы практического построения нейроморфных сетей связаны с током утечки через соседние элементы, паразитные сопротивление соединительных дорожек, необходимость разработки периферийных схем управления и алгоритмов системного уровня [58].

### 6.1. Ток утечки через соседние элементы

Проблема токов утечки через соседние элементы (sneak path) в структуре кросбара является ключевой, особенно, при высокой плотности элементов. В такой структуре, осуществляющей параллельные вычисления, становится сложным обратится к конкретному устройству. Например, для переключения состояния мемристора M1 (рис. 19) [59] необходимо подать напряжение между линиями кросбара A1 и B1. Однако в та-

ком случае, ток потечет не только через выбранный мемристор M1 (синяя линия), но и через соседние M2, M4 и M3 (красная линия).

Проблема тока утечки через соседние элементы может приводить к неправильному считыванию состояний мемристоров, кроме того, неконтролируемо влияет на состояние проводимости соседних элементов.

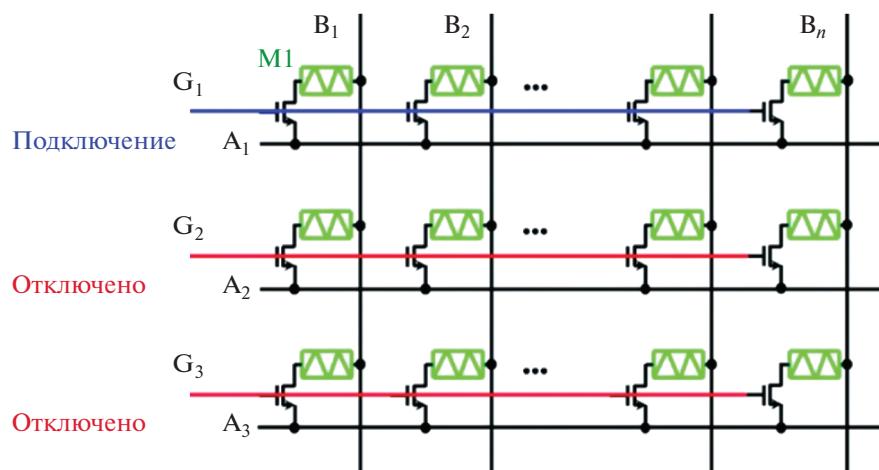

Чаще всего, для решения проблемы sneak path применяется транзистор, последовательно соединенный с мемристорным устройством, в каждом узле кросбара. В структуре 1T1R затвор транзистора подключается к линии слов (G), исток заземляется (A), электрод мемристора подключается к линии битов (B) (рис. 20). Такое решение позволяет программировать и читать состояния только выбранных элементов, но сильно усложняет устройство кросбара.

Также проблему sneak path можно решить при помощи структур 1D1M, 1S1M или специальных мемристоров с асимметричными характеристиками [60].

### 6.2. Высокое сопротивление дорожек

Для кросбара структур, по мере увеличения плотности элементов, все более значительной становится проблема высоких сопротивлений узких проводящих дорожек. Из-за паразитных сопротивлений дорожек в системе могут возникать RC задержки и неоднородности распределения потенциала, которые приводят к неправильной работе устройств, удаленных от источника питания.

Решить эти проблемы можно с помощью увеличения геометрических размеров проводящих дорожек, использования мемристора, сопротивление которого намного больше сопротивления дорожек, или перехода к новым материалам, на-

Рис. 20. 1T1R структура в кросбаре для решения проблемы sneak path [59].

Таблица 2. Ограничения и требования к различным архитектурам нейроморфных систем [44]

| Алгоритм        | Применение и результаты моделирования                            | Требования к устройству                                                                   | Преимущества                                                                               | Ограничения                                                                   |

|-----------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| SNN             | Распознавание рукописных цифр (82%) и букв (99%)                 | Синаптическая пластичность                                                                | Более биореалистичный, управляемый пространственно-временными событиями, энергоэффективный | Отсутствие высокоэффективных алгоритмов обучения и данных на основе импульсов |

| ANN (один слой) | Распознавание рукописных цифр (83%) и распознавание лиц (88.08%) | Аналоговая проводимость                                                                   | Высокая скорость                                                                           | Ограничивается простыми задачами                                              |

| ANN (два слоя)  | Простое распознавание цифр (100%)                                | Аналоговая проводимость                                                                   | Решает относительно более сложные задачи                                                   | Требуется многослойное вычисление градиента ВР                                |

| CNN [62]        | Распознавание рукописных цифр (94%)                              | Низкое энергопотребление, масштабируемость, аналоговая проводимость и длительное хранение | Решает очень сложные задачи                                                                | Проблемы с рассеиванием мощности и масштабируемостью                          |

| RNN             | Ассоциативное обучение и задача коммивояжера                     | Низкое энергопотребление, масштабируемость, аналоговая проводимость и длительное хранение | Ассоциативная память                                                                       | Требуется больше ресурсов для задач глубокого обучения                        |

пример, углеродным нанотрубкам, графену [61]. Эти меры снижают плотность размещения элементов на чипе и препятствуют миниатюризации структуры. Другой подход предполагает разделение единого большого массива элементов на множество небольших массивов. Таким образом можно снизить влияние паразитных сопротивлений и емкостей в каждом таком массиве. Возникает проблема компромисса между высокой вероятностью ошибок в работе нейронной сети, масштабированием, и эффективностью системы.

### 6.3. Необходимость периферийных схем

В настоящее время достаточно мало исследований посвящено развитию и интеграции периферийных устройств необходимых для нейроморфных систем. Большая часть исследований в области аналоговых вычислений сосредоточена на интеграции массивов устройств и в них редко оптимизируется конструкция периферийных устройств.

Можно перечислить наиболее часто используемые периферийные схемы: цифро-аналоговые (ЦАП) и аналого-цифровые (АЦП) преобразова-

тели, мультиплексоры, сумматоры, регистры ввода-вывода. Компоненты объединяются на одной или нескольких платах. Периферийные схемы большинства прототипов концептуальных устройств основаны на КМОП технологии, которая предполагает использование технологических процессов кремниевых ИС. Однако, КМОП технология может быть несовместима с мемристорами и новыми материалами, а это накладывает серьезные ограничения на разработку.

Цифро-аналоговые и аналого-цифровые преобразования связаны с ограничением энергопотребления и точности вычислений системы. На АЦП и ЦАП приходится до 60% энергопотребления всей системы [62]. Снижение точности при работе нейроморфных систем устраняют, добавляя дополнительные схемы компенсации или использованием гибридных технологий [63].

### 6.4. Ограничения и требования к архитектуре для различных алгоритмов

Выбор периферийных схем, технологий, материалов и структуры кроссбаров для архитектуры

нейроморфной системы определяется реализуемым в ней алгоритмом. В табл. 2 представлены ограничения и требования к архитектурам для самых распространенных алгоритмов.

## ЗАКЛЮЧЕНИЕ

Архитектура фон Неймана имеет множество плюсов и остается основным вариантом для реализации алгоритмов различного назначения. Именно для архитектуры фон Неймана написано большинство языков программирования, и даже новые решения и алгоритмы адаптируют под работу такой архитектуры. Чтобы новая архитектура могла конкурировать с архитектурой фон Неймана, она должна обладать огромным преимуществом.

Архитектуры нейроморфных систем могут составить конкуренцию архитектуре фон Неймана в отдельных областях. В основном речь идет о бурно развивающейся области приложений искусственного интеллекта и машинного обучения, например, о различных задачах алгоритмов нейронных сетей, например, классификации или распознавании образов. Именно такие задачи могут быть решены наиболее эффективно с помощью нейроморфных систем.

Основные направления исследований архитектур нейроморфных систем можно разделить на две области: оптимизация структуры периферийных схем архитектуры и разработка синаптических элементов нейроморфных систем. Если пока рано говорить о существенных успехах в оптимизации периферийных схем, то характеристики мемристоров и сегнетоэлектрических транзисторов, полученные в последнее время, позволяют надеяться на скорое появление эффективных кроссбаров на основе этих приборов и промышленной технологии их изготовления. Однако, перед этим необходимо решить ряд проблем, связанных с током утечки через соседние элементы и высоким сопротивлением дорожек в плотных кроссбараах.

## БЛАГОДАРНОСТИ

Работа выполнена в рамках Государственного задания ФТИАН им. К.А. Валиева РАН Минобрнауки РФ по теме № FFNN-2022-0019.

## СПИСОК ЛИТЕРАТУРЫ

1. *Shipley C., Jodis S.* in Encyclopedia of Information Systems, 2003

2. Принципы фон Неймана (Архитектура фон Неймана) // Планета Информатики URL: <https://infl.info/machinenemann> (дата обращения: 26.05.2022).

3. Симонов Н.А. Концепция пятен для задач искусственного интеллекта и алгоритмов нейроморфных систем // Микроэлектроника, 2020. Т. 49. № 6. С. 459–473.

4. *Jeong D.S., Kim K.M., Kim S., Choi B.J., Hwang C.S.* Memristors for Energy-Efficient New Computing Paradigms // *Adv. Elect. Mater.* 2, 1600090 (2016).

5. *Mead C.* Neuromorphic electronic systems // *Proc. IEEE* 78, 1990, 1629–1636.

6. *Ivanov D., Chezhegov A., Kiselev M.* Neuromorphic artificial intelligence systems // *Frontiers in Neuroscience*. 2022.

7. *Sung C., Hwang H., Yoo I.K.* Perspective: A review on memristive hardware for neuromorphic computation // *J. of Appl. Phys.* 2018. № 124.

8. *Feldman D.E.* The spike timing dependence of plasticity // *Neuron*, 2012, 75, 556–571.

9. *Gjorgjieva J., Clopath C., Audet J., Pfister J.P.* A triplet spike-timing-dependent plasticity model generalizes the Bienenstock-Cooper-Munro rule to higher-order spatiotemporal correlations // *Proc. Natl.*

10. *Ракитин В.В., Русаков С.Г.* Мемристорный генератор последовательности импульсов // Микроэлектроника, 2019. Т. 48. № 4. С. 300–307.

11. *Diehl P.U., Neil D, Binas J., Cook M., Liu S.-C., Pfeiffer M.* International Joint Conference on Neural Networks (IJCNN) (Killarney, Ireland), 2015. P. 1–8.

12. *Sengupta A., Ye Y., Wang R., Liu C., Roy K.* Front. Neurosci. 2019, 13, 95.

13. *de S. Dias C., Butzen P.F.* Memristors: A Journey from Material Engineering to Beyond Von-Neumann Computing // *J. of Integrated Circuits and Systems*, 2021. V. 16. № 1. P. 1–15.

14. *Sun Z., Ambrosi E., Bricalli A., Ielmini D.* Logic Computing with Stateful Neural Networks of Resistive Switches // *Adv. Mater.* 2018, V. 30(38), 1802554.

15. *Borghetti J., Snider G.S., Kuekes P.J.* ‘Memristive’ switches enable ‘stateful’ logic operations via material implication // *Nature*. 2010. № 464. P. 873–876.

16. *Talati N., Gupta S., Mane P., Kvatinsky S.* Logic Design Within Memristive Memories Using Memristor-Aided loGIC (MAGIC) // *IEEE*. 2016. № 15. P. 635–650.

17. *Kvatinsky S. et al.* MAGIC—Memristor-aided logic // *IEEE Transactions on Circuits and Systems II: Express Briefs*, 2014, V. 61(11). P. 895–899.

18. *Trepel M.* Neur Anat: Struktur und Funktion, 5. Auflage, Urban & Fischer, Munchen, 2012.

19. *Глаголев С.М.* Как работает нейрон: учебное пособие. Москва: Московская гимназия на Юго-западе, 1993. 63 с.

20. *Дубынин В.А.* Мозг: как он устроен и работает: Конспект лекций. Москва: МГУ, 2018. 183 с.

21. *Гладков А.А.* Динамика вызванной активности нейронной сети культуры диссоциированных клеток гиппокампа мышей при электрической стимуляции: дис. канд. биол. наук: 03.03.01, Нижний Новгород, 2018. 146 с.

22. Гафаров Ф.М. Искусственные нейронные сети и приложения: учеб. пособие / Ф.М. Гафаров, А.Ф. Галимьянов. Казань: Изд-во Казан. ун-та, 2018. 121 с.

23. Тарик Р. Создаем нейронную сеть. 1-е изд. Москва: Вильямс, 2018. 272 с.

24. Lanza M., Wong P., Pop E. Recommended Methods to Study Resistive Switching Devices: WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim, 2018.

25. Пермякова О.О., Рогожин А.Е. Моделирование резистивного переключения в мемристорных структурах на основе оксидов переходных металлов // Микроэлектроника, 2020. Т. 49. № 5. С. 323–333.

26. Valov I., Waser R., Jameson J.R., Kozicki M.N. Electrochemical metallization memories—fundamentals, applications, prospects // Nanotechnology. 2011. № 22. P. 24.

27. Lee J., Lu W.D. On-demand reconfiguration of nanomaterials: When electronics meets ionics // Adv. Mater., 2018. № 30.

28. Pan F., Gao S., Chen C., Song C., Zeng F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance // Mater. Sci. Eng., 2014. № 83. P. 1–59.

29. Noe P., Vallee C., Hippert F., Fillot F., Raty J.-Y. Phase-change materials for non-volatile memory devices: From technological challenges to materials science issues // Semicond. Sci. Technol. 2018. № 33.

30. Тулина Н.А., Иванов А.А., Россоленко А.Н. Резистивные переключения в мезоскопических гетероструктурах на основе эпитаксиальных пленок  $\text{Nd}_{2-x}\text{Ce}_x\text{CuO}_{4-y}$  // Микроэлектроника. 2017. Т. 46. № 3. С. 197–202.

31. Eryilmaz S.B., Kuzum D., Jeyasingh R., Kim S., Brightsky M., Lam C., Wong H.-S.P. Brain-like associative learning using a nanoscale non-volatile phase change synaptic device array // Front. Neurosci. 2014. № 8.

32. He H.-K., Yang R., Zhou W., Huang H.-M., Xiong J., Gan L., Zhai T.-Y., Guo X. Photonic potentiation and electric habituation in ultrathin memristive synapses based on monolayer MoS<sub>2</sub> // Small. 2018. № 14.

33. Kim D., Lu H., Ryu S., Bark C.-W., Eom C.-B., Tsymbal E., Gruber A. Ferroelectric tunnel memristor // Nano Lett. 2012. № 12. P. 5697–5702.

34. Kim H.J., Baek Y.J., Choi Y.J., Kang C.J., Lee H.H., Kim H.M., Kim K.B., Yoon T.S. // Rsc Advances. 2013. № 3.

35. Seo K., Kim I., Jung S., Jo M., Park S., Park J., Shin J., Biju K. P., Kong J., Lee K., Lee B., Hwang H. // Nanotechnology. 2011. № 22.

36. Borghetti J., Snider G.S., Kuekes P.J., Yang J.J., Stewart D.R., Williams R.S. ‘Memristive’ switches enable “stateful” logic operations via material implication // Nature, 2010. V.464(7290). P. 873–876.

37. Xu N., Park T., Yoon K.-J. In-Memory Stateful Logic Computing Using Memristors: Gate, Calculation, and Application // Phys. Status Solidi RRL 2021, 2100208.

38. Wang Z. et al. Resistive switching materials for information processing // Nature Reviews Materials, 2020. P. 1–23.

39. Wright C.D., Hosseini P., Diosdado J.A.V. Beyond von-Neumann computing with nanoscale phase-change memory devices // Advanced Functional Materials 2013. V. 23(18). P. 2248–2254.

40. Hu M., Li H., Wu Q., Rose G.S. Hardware realization of BSB recall function using memristor crossbar arrays // in DAC Design Automation Conference. 2012. P. 498–503.

41. Oh S., Hwang H., Yoo I.K. Ferroelectric materials for neuromorphic computing // APL Materials, 2019. № 7. P. 091109.

42. Jerry M., Chen P.-Y., Zhang J., Sharma P., Ni K., Yu S., Datta S. Ferroelectric FET analog synapse for acceleration of deep neural network training, in International Electron Devices Meeting (IEDM), San Francisco, CA, 2–6 December 2017.

43. Saxena V. Neuromorphic computing: From devices to integrated circuits // J. Vac. Sci. Technol. 2021. № 39. P. 21.

44. Zhang Y., Wang Z., Zhu J. Brain-inspired computing with memristors: Challenges in devices, circuits, and systems // Appl. Phys. Rev. 2020. № 7. P. 24.

45. Ahmed T., Walia S., Mayes E.L.H. Time and rate dependent synaptic learning in neuro-mimicking resistive memories // Scientific Reports. 2019. № 9. P. 11.

46. Sathya R., Abraham A. Comparison of supervised and unsupervised learning algorithms for pattern classification // International J. of Advanced Research in Artificial Intelligence, 2013. V. 2(2). P. 34–38.

47. Kuzum D., Yu S., Wong H.P. Synaptic electronics: materials, devices and applications // Nanotechnology, 2013. V. 24(38). P. 382001.

48. Wu X., Saxena V., Zhu K. A CMOS spiking neuron for dense memristor-synapse connectivity for brain-inspired computing // in 2015 International Joint Conference on Neural Networks (IJCNN), 2015. P. 1–6.

49. Ielmini D., Wang Z., Liu Y. Brain-inspired computing via memory device physics // APL Materials. 2021. № 9. 050702.

50. Hu S.G., Wu S.Y., Jia W.W. Review of Nanostructured Resistive Switching Memristor and Its Applications // Nanoscience and Nanotechnology Letters. 2014. № 6. P. 729–757.

51. Loihi – Intel // WikiChip URL: <https://en.wikichip.org/wiki/intel/loihi> (дата обращения: 26.05.2022).

52. Davies M., Srinivasa N., Lin T.-H. Loihi: A Neuromorphic Manycore Processor with On-Chip Learning // IEEE Computer Society 0272-1732/18. 2018.

53. Blouw P., Choo X., Hunsberger E., Eliasmith C. Benchmarking Keyword Spotting Efficiency on Neuromorphic Hardware // Applied Brain Research, Inc. Waterloo, ON, Canada. 2019.

54. Dharmendra S. Modha, TrueNorth: Accelerating From Zero to 64 Million Neurons in 10 Years. IEEE Computer, May 2019, IEEE Computer Society.

55. Merolla P.A., Arthur J.V., Alvarez-Icaza R., Cassidy A.S., Sawada J., Akopyan F. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface // Science, 2014. 345. P. 668–673.

56. *Ankit A., Ndu G., Rahul S.* Chalamalasetti PUMA: A Programmable Ultra-efficient Memristor-based Accelerator for Machine Learning Inference // Association for Computing Machinery. 2019.

57. *Baischer L., Wess M., TaheriNejad N.* Learning on Hardware: A Tutorial on Neural Network Accelerators and Co-Processors // 2021.

58. *Huang X., Liu C., Jiang Y.-G., Zhou P.* In-memory computing to break the memory wall // Chin. Phys. B. 2020. V. 29(7). P. 078504.

59. *Shi L., Zeng G., Tian B.* Research progress on solutions to the sneak path issue in memristor crossbar arrays // Nanoscale Advances. 2020. № 2. P. 1811.

60. *Huang C.H., Choi T.S., Huang J.S., Lin S.M., Chueh Y.L.* Self-Selecting Resistive Switching Scheme Using  $TiO_2$  Nanorod Arrays // Scientific Reports. 2017. № 7. P. 2066.

61. *Geim A.K., Novoselov K.S.* The rise of graphene Co-Published with Macmillan Publishers Ltd, UK 11-19, 2009.

62. *Yao P., Wu H., Gao B. et al.* Fully hardware-implemented memristor convolutional neural network // Nature, 2020. V. 577. P. 641–646.

63. *Cai F., Correll J.M., Lee S.H. et al.* A fully integrated re-programmable memristor–CMOS system for efficient multiply–accumulate operations // Nat Electron, 2019. V. 2. P. 290–299.