## ВЛИЯНИЕ ДЕГРАДАЦИИ ГОРЯЧИХ НОСИТЕЛЕЙ НА ХАРАКТЕРИСТИКИ ВЫСОКОВОЛЬТНОГО КНИ ТРАНЗИСТОРА С БОЛЬШОЙ ОБЛАСТЬЮ ДРЕЙФА

© 2023 г. А. С. Новоселов<sup>1</sup>, \*, Н. В. Масальский<sup>1</sup>

<sup>1</sup>Федеральное государственное учреждение Федеральный научный центр

Научно-исследовательский институт системных исследований РАН, Москва, Россия

\*E-mail: volkov@niisi.ras.ru

Поступила в редакцию 10.05.2023 г.

После доработки 10.07.2023 г.

Принята к публикации 10.07.2023 г.

Обсуждаются результаты исследования влияния деградации горячих носителей на электрофизические характеристики мощных LDMOS (laterally-diffused metal-oxide semiconductor) транзисторов, выполненных по технологии “кремний на изоляторе”, с длинной областью дрейфа с топологическими нормами 0.5 микрон. Анализ деградации горячих носителей в высоких электрических полях выполнен на основании экспериментальных результатах и дополнительном использовании аналитической модели. Физическое происхождение данного механизма связано с образованием ловушек на границе раздела Si/SiO<sub>2</sub>. С помощью численного анализа и экспериментов электрические характеристики КНИ nLDMOS-транзисторов рассмотрены в широком диапазоне управляющих напряжений с целью изучения влияния на зону безопасной эксплуатации и надежность устройства в условиях деградации горячих носителей. Результаты этих исследований позволяют сделать вывод о возможности 20%-го расширения зоны безопасной эксплуатации.

**Ключевые слова:** мощный LDMOS, технология “кремний на изоляторе”, деградация горячих носителей, моделирование, тестирование

**DOI:** 10.31857/S0544126923700497, **EDN:** PZRDFC

### 1. ВВЕДЕНИЕ

Транзисторы LDMOS (laterally-diffused metal-oxide semiconductor) архитектуры отличаются специальной конструкцией с оптимизированными характеристиками надежности, чтобы выдерживать высокие внешние электрические поля. С одной стороны, масштабирование КМОП технологии неизбежно приводит к нестабильности переноса горячих носителей в сильных электрических полях, что является критической проблемой, уже влияющей на производительность электронных схем в течение длительного времени работы [1]. С другой стороны, высокое рабочее напряжение само по себе делает устройства LDMOS особенно восприимчивыми к деградации горячих носителей при предельных режимах работы. Кроме того, из-за особенностей аналоговых/смешанных приложений вводятся более строгие стандарты надежности (широкие температурные диапазоны, длительный срок службы и надежность) [2]. Поэтому детальный анализ физических процессов связанных с деградацией горячих носителей в высоких электрических полях важен для определения долгосрочной зоны безопасной эксплуатации [3].

Исследование деградации горячих носителей в высоких электрических полях (в дальнейшем будем употреблять сокращение ДГН) обычно проводится в условиях постоянного напряжения и температуры окружающей среды. Обычно наихудшее условие анализируется при низком затворном напряжении  $U_{gs}$ , следуя подходу, применяемому к стандартным КМОП-устройствам [4, 5]. Однако, простых статических тестов на деградацию постоянного тока, проводимых только в наихудших случаях, может быть недостаточно для точного прогнозирования общей деградации схем на основе LDMOS транзисторов, в то время как наличие модели деградации LDMOS транзистора может быть востребовано [3, 5].

ДГН при  $U_{gs}$  ниже порогового характеризуется сдвигом тока стока в течение длительного времени при напряжении на стоке ( $U_{ds}$ ), достаточно высокого, чтобы достичь начала ударной ионизации [6]. В LDMOS транзисторах ток стока снижается главным образом за счет интерфейсных ловушек, которые генерируются во время действия внешнего электрического поля [7, 8]. Движущими силами, ответственными за образование ловушки

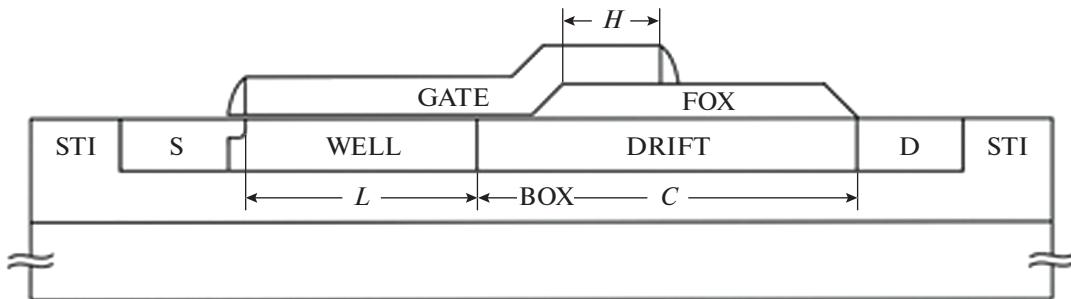

Рис. 1. Структурная схема высоковольтного КНИ LDMOS транзистора.

являются компоненты электрического поля, поскольку они строго связаны с вероятностью инжекции носителей и распределением горячих носителей. Деградацию можно отнести к термически активированному повреждению [9, 10]. При этом наблюдается значительное повышение температуры решетки вдоль границы раздела Si/SiO<sub>2</sub>.

В настоящей работе на основе экспериментальных и расчетных данных исследуется влияние ДГН на электро-физические характеристики высоковольтного КНИ LDMOS транзистора с длинным каналом и длинной областью дрейфа. Мы модифицировали модель расчета ВАХ, дополнив ее моделью ДГН на ловушках из-за разорванных связей на границе DRIFT-FOX, тем самым обеспечив возможность моделировать кинетику генерации ловушек и изменение ВАХ со временем. Определили тенденции снижения тока стока, рост напряжения пробоя в диапазоне окружающих температур 300–400 К.

## 2. СТРУКТУРА ТРАНЗИСТОРА

Схема поперечного сечения высоковольтного КНИ LDMOS транзистора, используемого в этом исследовании, показана на рис. 1 [11], а характеристики легирования в табл. 1. В анализируемом устройстве длина канала  $L$  составляет 1.5 мкм, область дрейфа (DRIFT)  $n$ -типа примерно в четыре раза больше – ее длина  $C$  составляет 7 мкм. Эта об-

ласть определяет и напряжение пробоя. Электрод затвора (GATE) покрывает поверхность канала и часть области дрейфа. Рабочая область транзистора изолирована от подложки толстым оксидом кремния BOX. Это обеспечивает диэлектрическую изоляцию и сводит к минимуму паразитные явления.

## 3. ДГН ПРИ НИЗКИХ $U_{gs}$

В литературе были предложены различные физические механизмы для объяснения ДГН в высоковольтных транзисторах, с учетом специфической роли горячих электронов и дырок и природы разорванных связей (Si–H или Si–O) (см., например, [12]). Чтобы смоделировать влияние ДГН, строгий подход должен основываться на численном решении полно-диапазонного уравнения переноса Больцмана [12, 13]. Предлагаемые инструменты моделирования методом Монте-Карло очень трудоемки и применяются только к простым структурам устройств и/или ограниченным пространственным областям [14–16]. Применение такого подхода ко всей области устройств мощных LDMOS по-прежнему недоступно.

Можно рассмотреть подход, основанный на менее строгих, но эффективных методологиях. Модель деградации основана на решении кинетического уравнения реакции–диффузии. Последнее представляет собой хорошую отправную

Таблица 1. Уровни легирования областей транзистора

| № | Наименование области | Легирующая примесь | Уровень легирования, 1/см <sup>3</sup> |

|---|----------------------|--------------------|----------------------------------------|

| 1 | PWELL                | Бор                | 2.0E + 17                              |

| 2 | NWELL                | Фосфор             | 2.5E + 17                              |

| 3 | PLDD                 | Бор                | 9.0E + 18                              |

| 4 | NLDD                 | Фосфор             | 1.1E + 19                              |

| 5 | PPLUS                | Бор                | 1.5E + 20                              |

| 6 | NPLUS                | Фосфор             | 2.0E + 20                              |

| 7 | PDRIFT               | Бор                | 2.0E + 17                              |

| 8 | NDRIFT               | Фосфор             | 2.5E + 17                              |

точку для точного описания образования межфазной ловушки в любом напряженном состоянии, при условии, что коэффициенты уравнения, которые дают скорости реакции разрыва связи, определены с помощью точных моделей. Модель скорости реакции основана на приближении Аррениуса с эмпирическими зависимостями от электрических полей и плотностей горячих носителей [17–19]. Таким образом, этот подход может быть успешно использован для понимания деградации при низких смещениях без эффектов самонагревания [19, 20].

Исходя из кинетики первого порядка, феноменологическое уравнение скорости генерации ловушки на границе раздела можно записать в виде [17]:

$$\frac{dN_{it}}{dt} = k(N_0 - N_{it}), \quad (1)$$

где  $N_0$  – максимальное количество межфазных связей,  $N_{it}$  – количество разорванных связей (соответствует плотности межфазной ловушки),  $k$  – скорость прямой реакции разрыва связи.

Из общих положений кинетики отметим, что одновременно могут присутствовать два конкурирующих механизма, ответственных за разрыв связей: одноэлектронный и многоэлектронный процессы [1, 21]. Для низкого уровня  $U_{gs}$  основную роль играют одноэлектронные процессы. Модели, описанные в [2, 12], были использованы для расчета индивидуального вклада в  $N_{it}$  как функции времени стресс-теста  $t_s$  и пиковой энергии активации  $E_a$ . Стресс-тесты проводятся путем фиксации напряжения смещения и температуры окружающей среды  $T_A$ . Подача напряжения периодически прерывается для измерения ухудшения параметров транзистора в подпороговом режиме при одной и той же температуре окружающей среды. Экспериментальные результаты не показали какого-либо значительного восстановления при устраниении напряженного состояния; таким образом, вклад обратной реакции не учитывался. Скорость  $k$  может быть определена соответствующим интегралом рассеяния, зависящим от энергии активации связи на границе раздела Si/SiO<sub>2</sub>, функции распределения электронов, их плотности состояний и групповой скорости, поперечного сечения реакции, эффективного дипольного момента и температуры решетки [14, 19, 21]. Необходимо отметить, что для одноэлектронного процесса использовались значения параметров, аналогичные тем, о которых сообщалось в работах [8–10, 22], близких к теоретическим результатам [1, 3, 19, 23]. В итоге решение (1) можно преобразовать к следующему виду [19]:

$$N_{it}(t) = N_0 \int_{E_a-3\sigma}^{E_a+3\sigma} dE g_A(E)(1 - e^{-k(E)t}), \quad (2)$$

где распределение  $g_A(E)$ , заданное производной функции Ферми, расширение распределения характеризуется шириной дисперсии  $\sigma$ .

Дисперсия энергии активации смещает профили  $N_{it}$  в сторону более высоких значений. Это становится очевидным, учитывая, что колебания  $E_a$  обеспечивают более низкие энергии активации, в то время как, поверхностная плотность ловушек возрастает при более низких энергиях. В результате взаимодействия этих эффектов может быть возбуждено больше связей, как если бы  $E_a$  была зафиксирована на определенном значении.

Следует отметить, что при моделировании прямое туннелирование через оксид затвора предполагается незначительным, поскольку используются относительно толстые пленки. Поэтому, деградацией из-за эффектов утечки тока можно пренебречь, и учитывать только термическую деградацию.

Дополнительные локализованные заряды, создаваемые таким образом на границе раздела оксид/DRIFT, могут изменять поверхностный потенциал, что может повлиять на характеристики устройства, включая ток стока, изменения кратчайший путь переноса носителей [23–25]. Следовательно, эффекты этих локализованных зарядов нельзя игнорировать при моделировании электрических характеристик. В данном случае рассматривается квазианалитическое моделирование распределения поверхностного потенциала, и связанного с ним распределения электрического поля, и тока стока путем включения межфазных захваченных зарядов из-за наличия усиленного электрического поля в транзисторе, главным образом в DRIFT-области. Поверхностный потенциал получен путем решения двумерного уравнения Пуассона, которое затем используется для определения электрического тока в подпороговом режиме устройства.

#### 4. МОДЕЛИРОВАНИЕ ВЛИЯНИЯ ДГН

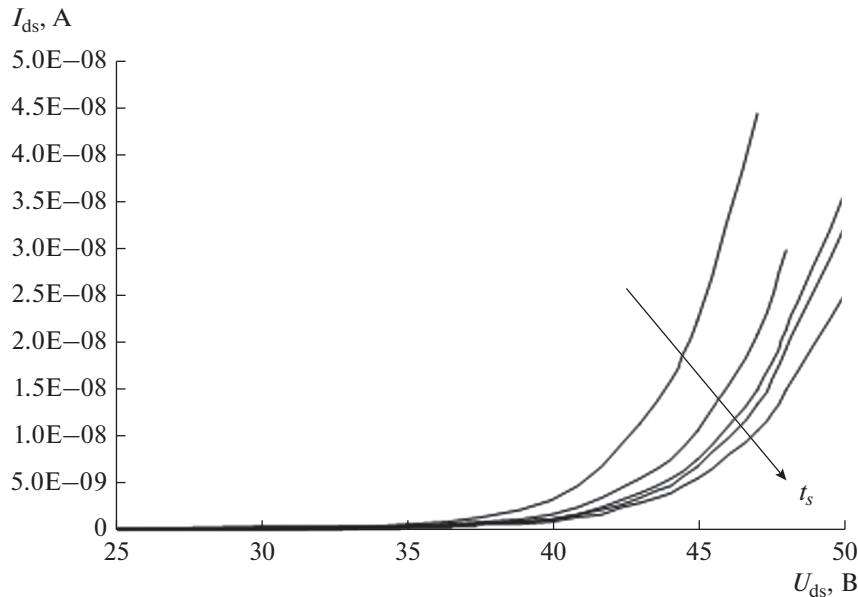

При низком  $U_{gs}$ , дрейф тока стока транзистора отслеживался в течение длительного времени при изменении напряжения на стоке  $U_{ds}$  в диапазоне выше 25 В. Пример ВАХ  $I_{ds}(U_{ds})$  для анализируемого устройства (длинно-канального LDMOS с большой областью дрейфа) показан на рис. 2.

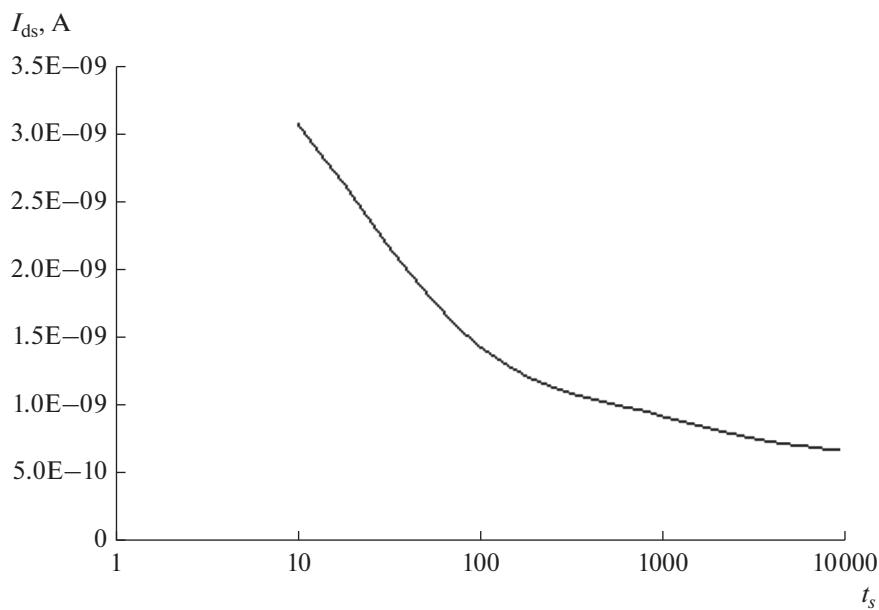

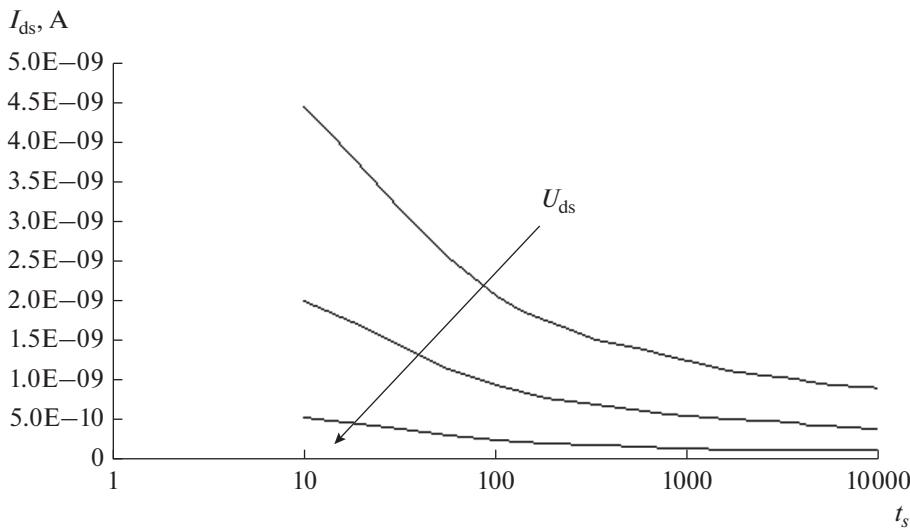

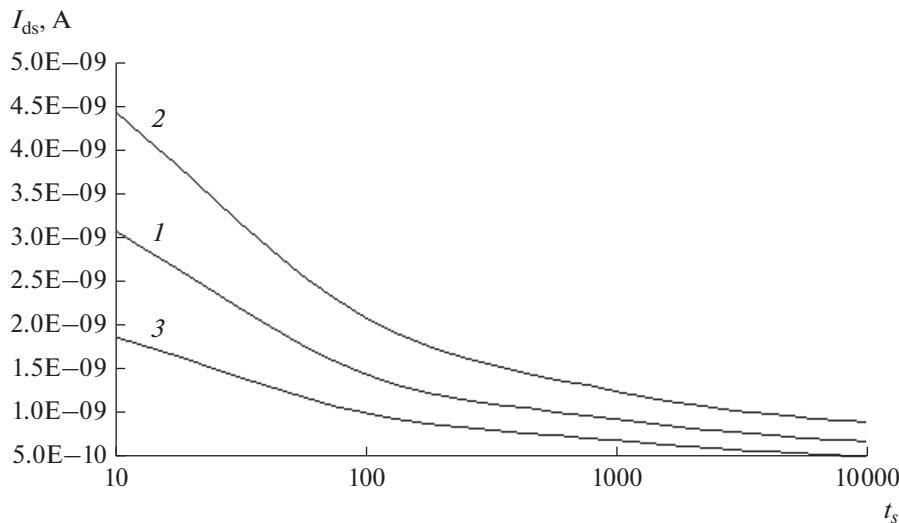

В устройствах LDMOS ток стока снижается, что иллюстрируется рис. 3–5, главным образом за счет генерируемых интерфейсных ловушек в зависимости от количества отсчетов (стресс-теста). Это также экспериментально подтверждается сдвигом порогового напряжения, которое является незначительным, указывая, что граница раздела затвор-оксид в области канала не ухудшается из-за наличия механизма ДГН.

Полученные результаты характеризуют временной дрейф тока стока транзистора из-за меха-

Рис. 2. ВАХ  $I_{ds}(U_{ds})$   $U_{gs} = 0$  для разных времен отсчетов  $t_s$ , где самая верхняя  $t_s = 10$ , далее 100, 1000, 5000, 10000.

Рис. 3.  $I_{ds}(U_{ds} = 40 \text{ V}, U_{gs} = 0)$  от  $t_s$ . Здесь и ниже временная ось в лог-масштабе.

низма ДГН в диапазоне подпороговых затворных напряжений и напряжений на стоке близких к напряжению пробоя. Можно утверждать, что после  $1000/t_s$  дрейф значительно снижается и в конечном итоге он может достигнуть насыщения, что требует экспериментальной проверки.

Из результатов моделирования следует, что эффект снижения энергии активации становится менее выраженным при длительном стресс-тесте и при более высоких  $U_{ds}$ . При этом, возможный статистический разброс в  $E_a$  может существенно

усиливать ДГН, хотя это влияние менее выражено при более высоких стоковых напряжениях. Этот вывод представляется обоснованным, поскольку, если носители уже достаточно горячие, дальнейшее снижение энергии активации не приведет к дополнительному разрыву связей.

## 5. НАПРЯЖЕНИЕ ПРОБОЯ

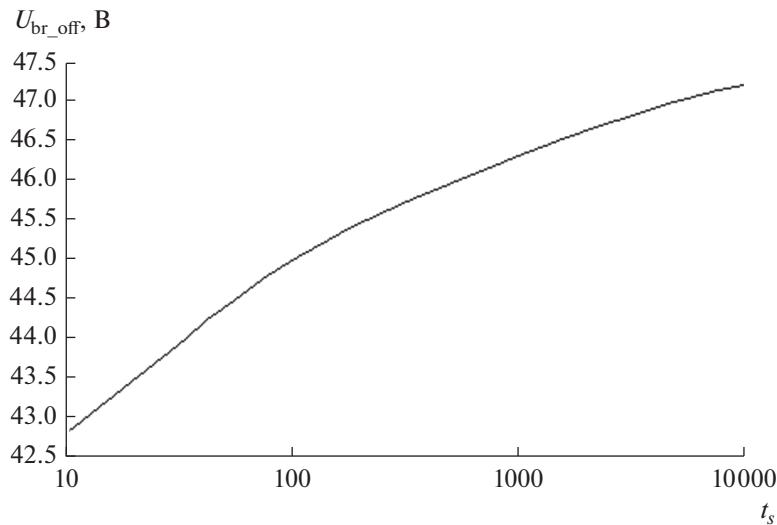

Дрейф тока стока обуславливает соответствующий рост напряжения пробоя транзистора в за-

Рис. 4.  $I_{ds}(U_{ds}, U_{gs} = 1)$  от  $t_s$ , где  $U_{ds} = 40$  В, 38 В, 36 В.Рис. 5.  $I_{ds}(U_{ds} = 40$  В,  $U_{gs} = -1; 0; 1)$  от  $t_s$ , где 1 –  $U_{gs} = 0$  В, 2 –  $U_{gs} = 1$  В, 3 –  $U_{gs} = -1$  В.

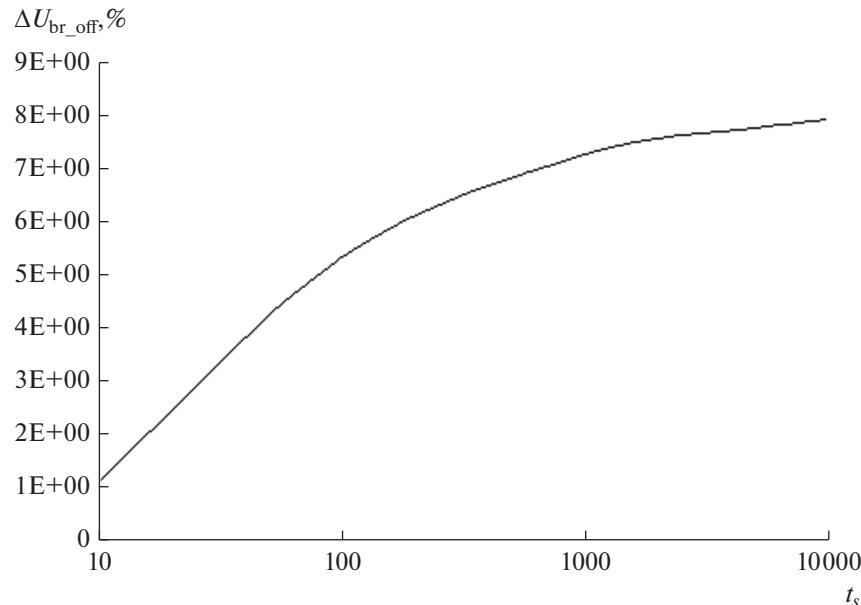

крытом состоянии ( $U_{br\_off}$ ). Его значение определяется по уровню тока стока 10 нА. Временная зависимость, экстрагированная из рис. 2 приведена на рис. 6.

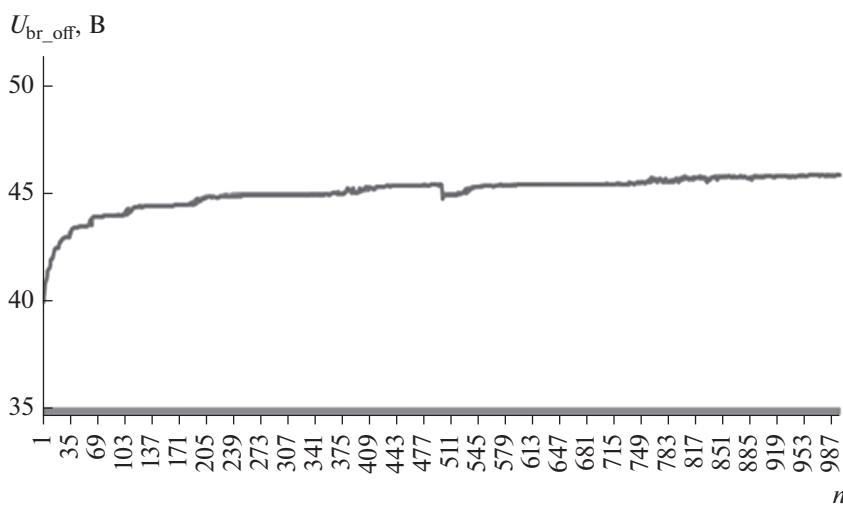

Аналогичная зависимость была получена экспериментально. Мы проводили измерение пробивного напряжения по уровню тока 10 нА в два этапа: 1 этап – 500 циклов измерения  $U_{br\_off}$ ; 2 этап – через 5 дней еще 500 циклов измерения  $U_{br\_off}$ . Итого 1000 циклов измерения. На рис. 7 приведен график изменения пробивного напряжения от количества циклов (скачок вниз – начало 2 этапа).

Сопоставление расчетных и экспериментальных данных говорит о их хорошем согласовании. Из приведенных данных видно, что дальнейшие

стресс-тесты, после 1000 с, не приводят к заметному росту параметра  $U_{br\_off}$ . Их 10-кратное увеличение предопределяет рост на 0.9 В. В отличии от первого этапа, где  $U_{br\_off}$  увеличилось на 2.5 В.

## 6. РАСШИРЕНИЕ ДОЛГОСРОЧНОЙ ЗОНЫ БЕЗОПАСНОЙ ЭКСПЛУАТАЦИИ

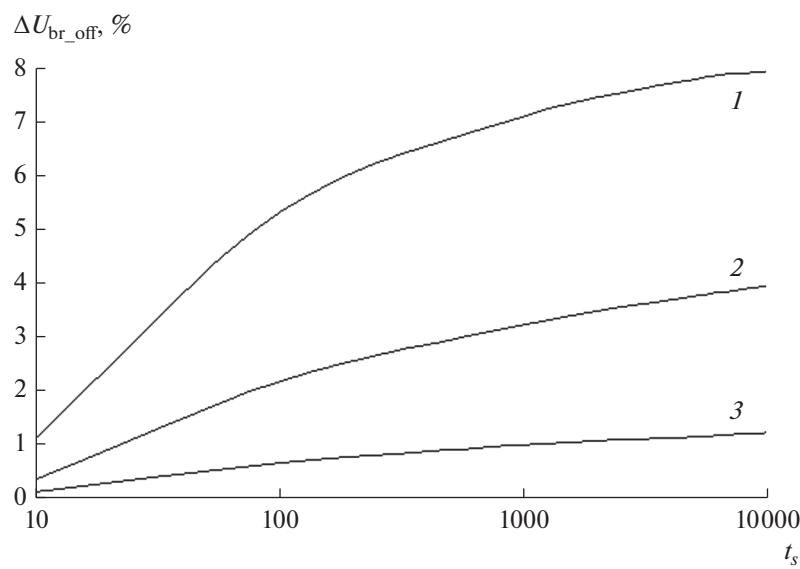

С помощью рассмотренной методики моделирования аналогичные расчеты ВАХ  $I_{ds}(U_{ds})$  в подпороговом режиме были проведены для повышенной температуры окружающей среды. Для ключевой характеристики  $U_{br\_off}$  получены следующие результаты, представленные ниже на рис. 8. В общем случае повышение температуры  $T_A$  приво-

Рис. 6. Напряжение пробоя  $U_{\text{br\_off}}$  от  $t_s$ .Рис. 7. Экспериментальные данные: напряжение пробоя ( $U_{\text{br\_off}}$ ) от кол-ва циклов ( $n$ ).Рис. 8. Изменение напряжение пробоя (%) от  $t_s$  при разной температуре  $T_A$ , где 1 – 300 К, 2 – 350 К, 3 – 400 К.

Рис. 9. Изменение напряжение пробоя (%) от  $t_s$  для разных длин области дрейфа.

дит к уменьшению самой деградации, главным образом из-за общего уменьшения пика электрического поля. Чтобы отследить влияние ДГН, изменение  $U_{br\_off}$  представлено в процентах к усредненному значению  $U_{br\_off}$  первых трех отсчетов. Из полученных данных видно, что влияние сохраняется, но его эффективность падает с ростом температуры. Гипотетически можно достичь тех же процентных соотношений для  $U_{br\_off}$ , однако время будет очень большим (будет иметь поистине космические масштабы!), что, вероятно, будет превышать ресурс устройства. Подчеркнем, реперное значение  $U_{br\_off}$  также зависит от температуры, что является экспериментально доказанным фактом.

Аналогичные расчеты были проведены для увеличенной области дрейфа. Проанализировано дополнительно три значения  $C = 8.0, 9.0, 9.5 \text{ мкм}$  и постоянное значение  $H = 1 \text{ мкм}$  при  $T_A = 300 \text{ К}$ . Аналогичное процентное представление изменения  $U_{br\_off}$ , представленное на рис. 9, определило, что влияние ДГН практически одинаково для анализируемых прототипов.

Приведенные данные позволяют сделать вывод о возможности 20% расширения долгосрочной зоны безопасной эксплуатации высоковольтного длинноканального nLDMOS по окружающей температуре и геометрии области дрейфа.

## ЗАКЛЮЧЕНИЕ

Исследовано влияния деградации горячих носителей на электрофизические характеристики мощных КНИ nLDMOS транзисторов с длинной областью дрейфа с топологическими нормами

0.5 микрон. Физическое происхождение данного механизма связано с образованием ловушек на границе раздела Si/SiO<sub>2</sub> в сильных электрических полях. Адаптирована физическая модель деградации горячих носителей для уточнения процесса переноса носителей в высоковольтном nLDMOS транзисторе. Модель способна представлять линейное изменение тока стока при затворных напряжениях ниже порогового при различных значениях напряжения на стоке и времени стресс-теста. Проанализирована зависимость напряжения пробоя от времени стресс-теста, температуры окружающей среды и увеличенной области дрейфа. Результаты этих исследований позволяют сделать вывод о возможности 20%-го расширения зоны безопасной эксплуатации.

## КОНФЛИКТ ИНТЕРЕСОВ

У авторов нет конфликта интересов, имеющих отношение к содержанию данной рукописи.

## БЛАГОДАРНОСТИ

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН Проведение фундаментальных научных исследований (47 ГП) по теме НИР “Фундаментальные и прикладные исследования в области литографических пределов полупроводниковых технологий и физико-химических процессов травления 3D нанометровых диэлектрических структур для развития критических технологий производства ЭКБ. Исследование и построение моделей и конструкций эле-

ментов микроэлектроники в расширенном диапазоне температур (от  $-60$  до  $+300^{\circ}\text{C}$ ) (FNEF-2022-0006)".

## СПИСОК ЛИТЕРАТУРЫ

1. Bravaix A., Huard V., Cacho F., Federspiel X., Royl D. Hot-carrier degradation in decanometer CMOS nodes: From an energy driven to a unified current degradation modeling by multiple carrier degradation process, in *Hot-Carrier Degradation*, ed. By T. Grasser, Springer, Wien, New York, 2015.

2. Moens P., den Bosch G.V. Characterization of total safe operating area of lateral DMOS transistors // IEEE Trans Device Mater Rel. 2006. V. 6. P. 349–357.

3. Moens P., Varghese D., Alam M.A. Towards a universal model for hot carrier degradation in DMOS transistors. In: Proceedings of the international symposium on power semiconductor devices and ICs. Barcelona, Spain, 2010. P. 61–64.

4. Wang W., Reddy V., Krishnan A.T., Vattikonda R., Krishnan S., Cao Y. Compact modeling and simulation of circuit reliability for 65 nm CMOS technology // IEEE Trans Device Mater Rel. 2007. V. 7. P. 509–517.

5. Poli S., Reggiani S., Baccarani G., Gnani E., Gnudi A., Denison M. Hot-carrier stress induced degradation in multi-STI-finger LDMOS: an experimental and numerical insight // Solid-State Electron. 2011. 65–66. P. 57–63.

6. Bude J., Hess K. Thresholds of impact ionization in semiconductors // J. Appl. Phys. 1992. V. 72. P. 3554–3561.

7. Hu C., Tam S., Hsu F., Ko P., Chan T., Terrill K.W. Hot-electron-induced MOSFET degradation—model, monitor, and improvement // IEEE Trans Electron Devices. 1985. V. 32. P. 375–383.

8. Ancona M.G., Saks N.S., McCarthy D. Lateral distribution of hot-carrier-induced interface traps in MOSFETs // IEEE Trans Electron Devices. 1988. V. 35. P. 2221–2228.

9. Di Maria D.J., Stasiak J.W. Trap creation in silicon dioxide produced by hot electrons // J. of Appl. Phys. 1989. V. 65. P. 2342–2357.

10. Yassine A.M., Nariman H.E., McBride M., Uzer M., Oasupo K.R. Time dependent breakdown of ultrathin gate oxide // IEEE Trans Electron Devices. 2000. V. 47. P. 1416–1420.

11. Wang L., Wang J., Gao C., Hu J., Li P.Z.X., Li W., Yang S.H.Y. Physical description of quasi-saturation and impact ionization effects in high-voltage drain-extended MOSFETs // IEEE Trans. Electron Devices. 2009. V. 56. P. 492–498.

12. Varghese D., Kufluoglu H., Reddy V., Shichijo H., Moshier D., Krishnan S. OFF-state degradation in drain-extended NMOS transistors: interface damage and correlation to dielectric breakdown // IEEE Trans Electron Devices. 2007. V. 54. P. 2669–2677.

13. Varghese D., Moens P., Alam M.A. ON-state hot carrier degradation in drain-extended NMOS transistors // IEEE Trans. Electron Devices. 2010. V. 57. P. 2704–2710.

14. Hong S.-M., Pham A., Jungemann C. Deterministic solvers for the Boltzmann transport equation, Springer Science & Business Media, 2011.

15. Cheng S.-W., Dey T.K., Shewchuk J.R. Delaunay Mesh Generation. CRC Press, 2013.

16. Rudolf F., Weinbub J., Rupp K., Selberherr S. The meshing framework ViennaMesh for finite element applications // J. of Comp. and Appl. Mathematics. 2014. V. 167. P. 166–177.

17. Penzin O., Haggag A., McMahon W., Lyumkis E., Hess K. MOSFET degradation kinetics and its simulation // IEEE Trans. Electron Devices. 2003. V. 50. P. 1445–1450.

18. Reggiani S., Barone G., Gnani E., Gnudi A., Baccarani G., Poli S., Wise R., Chuang M.-Y., Tian W., Pendharkar S., Denison M. Characterization and modeling of electrical stress degradation in STI-based integrated power devices // Solid-State Electronics. 2014. V. 102. № 12. P. 25–41.

19. Reggiani S., Barone G., Gnani E., Gnudi A., Baccarani G., Poli S., Wise R., Chuang M.-Y., Tian W., Pendharkar S., Denison M. Characterization and modeling of high-voltage LDMOS transistors in book Hot carrier degradation semiconductor devices by ed T. Grasser, Springer Cham Heidelberg New York Dordrecht London, 2015. P. 309–340.

20. Rumyantsev S.V., Novoselov A.S., Masalsky N.V. Investigating the electro-thermal characteristics of partially depleted submicron SOI CMOS in an extended temperature range // Russian Microelectronics. 2020. V. 49. № 1. P. 30–36.

21. Guerin C., Huard V., Bravaix A. General framework about defect creation at the Si/SiO<sub>2</sub> interface // J. of Appl. Phys. 2009. V. 105. № 11. P. 114513.1–114513.12.

22. Stesmans A. Passivation of Pb0 and Pb1 interface defects in thermal (100) Si/SiO<sub>2</sub> with molecular hydrogen // Appl. Phys. Letters. 1996. V. 68. № 15. P. 2076–2078.

23. Sharma P. Modeling of hot-carrier degradation in nLDMOS devices: different approaches to the solution of the Boltzmann transport equation // IEEE Trans. Electron Devices. 2015. V. 62. № 6. P. 1811–1818.

24. de Jong M.J., Salm C., Schmitz J. Towards understanding recovery of hot-carrier induced degradation // Microelectronics Reliability. 2018. V. 88. P. 147–151.

25. Yu Z., Zhang Z., Sun Z., Wang R., Huang R. On the trap locations in bulk finFETs after hot carrier degradation (HCD) // IEEE Trans. Electron Devices. 2020. V. 67. P. 3005–3009.