Микроэлектроника, 2022, T. 51, № 3, стр. 230-240

Сбор заряда КМОП транзисторами с треков одиночных частиц, проходящих через слой мелкой траншейной изоляции

В. Я. Стенин a, b, *, Ю. В. Катунин a, **

a НИИ системных исследований Российской академии наук

Москва, Нахимовский проспект, 36, к. 1, Россия

b Национальный исследовательский ядерный университет “МИФИ”

Москва, Каширское шоссе, 31а, Россия

* E-mail: vystenin@mephi.ru

** E-mail: katunin@cs.niisi.ras.ru

Поступила в редакцию 21.10.2021

После доработки 23.12.2021

Принята к публикации 10.01.2022

- EDN: QMMCYK

- DOI: 10.31857/S0544126922030127

Аннотация

Проводится моделирование средствами 3D TCAD особенностей сбора неосновных носителей заряда, образованных на треках одиночных частиц в слое 200–250 нм кремния под мелкой траншейной изоляцией в КМОП двухвходовом элементе И-НЕ и инверторе в составе мажоритарного элемента. Исследуется сбор заряда группами из двух NМОП, двух PМОП транзисторов, а также одного PМОП транзистора при сборе заряда с треков с точками входа в кремниевые приборные области транзисторов и в окружающию мелкую траншейную изоляцию на расстояниях 40–700 нм от края групп транзисторов. Диапазон зарядов, перенесенных импульсами тока с этих расстояний, составляет от 50 до 4.5 фКл при LET = 60 МэВ · см2/мг и от 80 до 11 фКл при LET = 90 МэВ · см2/мг. Увеличение расстояния точки входа трека в траншейную изоляцию на 200 нм от области группы транзисторов, собирающих заряд с трека, снижает амплитудное значение импульса тока, переносящего заряд с трека, в 1.8–2.0 раза, а также снижает вдвое величину собранного заряда. При LET = 90 МэВ · см2/мг амплитудные значения импульсов напряжения на узле, выводящем заряд двумя NМОП или двумя PМОП транзисторами двухвходового элемента И-НЕ в диапазоне точек входа трека от 40 до 200 нм могут снижаться в 1.5–2.0 раза при увеличении расстояиия точки входа трека на 100 нм от края области транзисторов. Импульсы ошибок на выходе мажоритарного элемента с амплитудой 0.7–1 В образуются при точках входа трека непосредственно в область приборного кремния NМОП и PМОП транзисторов, а также при треках с точками входа в слой траншейной изоляции на расстоянии 40–100 нм от границы областей приборного кремния преимущественно при сборе заряда NМОП транзисторами.

1. ВВЕДЕНИЕ

Мелкая траншейная изоляция (Shallow Trench Isolation – STI) используется как конструктивно-технологическое средство для снижения “паразитной” взаимосвязи КМОП транзисторов на кристалле микросхем, в частности, для минимизации эффектов при воздействии ионизирующих излучений. КМОП микросхемы по стандартной объемной технологии 65 нм характерны тем, что в слое толщиной 200–250 нм кремния под мелкой траншейной изоляцией осуществляется перенос (диффузия) неосновных носителей заряда, образованных на треках одиночных частиц с точками входа треков в траншейную изоляцию. Встроенные электрические поля под мелкой траншейной изоляцией частично удерживают неосновные носители заряда в слое под диэлектриком на глубине от 400 до 650 нм, где и происходит диффузионный перенос неравновесных неосновных носителей заряда. Заряд, генерируемый на треке на глубинах более 650 нм, уходит в подложку. Задачи, связанные с исследованием траншейной изоляции, решались по мере снижения проектно-технологических норм.

Аналитическая модель [1] для расчета плотности поверхностного заряда вдоль боковой стенки траншейной изоляции подтвердила, что путь инверсии проходит значительно ниже угла траншеи для КМОП элементов с проектной нормой 180 нм. Повышенная надежность и характеристики устойчивости крупномасштабных устройств вызвана сочетанием более высоких уровней легирования и уменьшением бокового пути сбора заряда в траншее.

Исследование и сравнение эффективности методов разделения заряда для уменьшения сбора заряда соседними узлами в NМОП транзисторах по объемной технологии 65 нм проведено [2] с использованием 2D TCAD гибридного моделирования для определения заряда, собранного в смежном узле, примыкающем к транзистору, на который воздействовали тяжелыые ионы, для случаев использования мелкой траншейной изоляции (STI), глубокой траншейной изоляция (Deep Trench Isolation – DTI), защитного кольца или защитного диода при воздействии частиц с различной линейной энергией передачи (LET). В итоге, наибольшее снижение собранного заряда (более 98%) на соседнем узле характерно для глубокой траншейной изоляция. При использовании DTI практически нет увеличения площади кристалла, но есть небольшое расширение импульса помехи на узле, собирающем заряд с трека. Моделирование средствами TCAD показало также [2], что для 65-нм объемной КМОП технологии тяжелый ион при передаче на трек энергии 20 МэВ ⋅ см2/мг изменяет состояние не только активного транзистора, но и пассивного при расстоянии 160 нм от стока активного.

Моделирование перераспределения заряда в объеме мелкой траншейной изоляцией (STI) [3], вызванного воздействием излучения показывает, что вблизи верхней части траншеи удерживается гораздо меньше заряда, чем ожидалось. Установлено, что заряды внутри оксида STI вытесняются вертикальным электрическим полем, обусловленным положительным напряжением смещения затвора КМОП транзистора, что оставляет гораздо меньший суммарный заряд, индуцированный дозой, вблизи вершины траншеи. Эта неравномерность существенно влияет на ток утечки между транзисторами.

3D-моделирование показало [4], что длительность сбора заряда существенно коррелирует с длительностью импульса напряжения на узле, собирающем заряд с трека одиночной частицы. В результате исследования разницы между длительностями сбора заряда 90-нм NМОП и 55-нм NМОП транзисторами обосновано, что отличие в глубинах и ширине линии контакта p-кармана, присущих этим технологиям влияет в основном на длительность сбора заряда через величину сопротивления между каналом и контактом р-кармана. Уменьшить длительность сбора заряда можно путем модификации профиля кармана.

3D TCAD моделирование логических элементов ассоциативных запоминающих устройств на основе ячейки памяти STG DICE [5] при сборе ими зарядов с треков одиночных частиц с линейными переносом энергии до 60 МэВ · см2/мг показало, что есть разделение и сбор заряда смежными узлами на как на NМОП, так и на PМОП транзисторах по объемной технологии 65 нм при расстояниях до 300 нм от точек входа трека в мелкаую траншейную изоляцию до приборных областей кремния с транзисторами.

TCAD моделирование [6] сбора заряда с треков, проходящих поперек слоя, вдоль слоя, а также под слоем мелкой траншейной изоляции, используемой в объёмной 65-нм КМОП технологии, проведено на примере элемента памяти на основе ячейки памяти STG DICE с дополнительной комбинационной логикой чтения данных из такой ячейки памяти, находящейся в нестационарном состоянии при сборе заряда с трека. Моделирование проводилось при сборе зарядов с треков, проходящих через или ниже стоков взаимно чувствительных транзисторов на глубинах от 50 до 850 нм от поверхности кристалла и дополнительно при угловых отклонениях до 40°, что позволило установить влияние отклонений треков от обычно используемого направления по нормали к поверхности кристалла на амлитуды образующихся импульсов помех.

Цель представленного в данной работе исследования – моделирование количественных зависимостей мплитудных значений импульсов тока, импульсов напряжения на узлах с транзисторами, собирающими заряд, а также перенос заряда от треков с точками входа в мелкаую траншейную изоляцию до приборных областей кремния с транзисторами. Как объект для проведения исследования используется КМОП 3D TCAD модель мажоритарного элемента на основе И-НЕ логики с пониженной чувствительностью к воздействию одиночных ионизирующих частиц [7].

2. ТЕСТОВЫЙ ЭЛЕМЕНТ НА ОСНОВЕ ТРОЙНОГО МАЖОРИТАРНОГО ЭЛЕМЕНТА НА И-НЕ КМОП ЛОГИКЕ

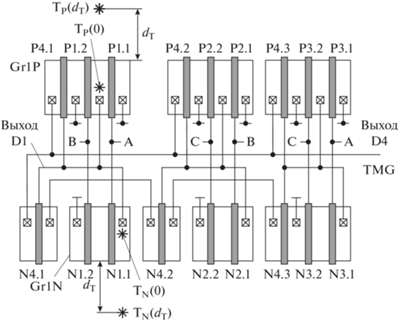

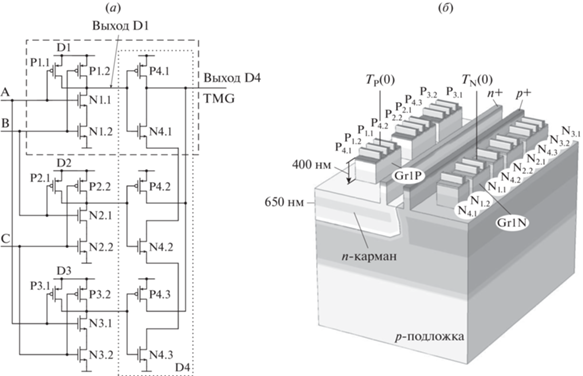

2.1. Схема элемента и особенности приборной 3D TCAD физической модели. Для моделирования переноса носителей заряда с трека одиночной частицы в работе используется тройной мажоритарный элемент [7], схема которого приведена на рис. 1а. Он состоит из трех двухвходовых КМОП элементов 2И-НЕ D1, D2, D3 и одного трехвходового элемента 3И-НЕ D4. Первая цифра в обозначениях транзисторов на рис. 1а соответствует номеру элемента D1, D2, D3 или D3, а вторая – номеру транзистора в этих элементах.

Рис. 1.

КМОП тройной мажоритарный элемент на И-НЕ логических элементах: (а) схема; (б) приборная 3D TCAD физическая модель, использованная при моделировании КМОП тройного мажоритарного элемента на И-НЕ логических элементах.

На рис. 1б приведен эскиз приборной 3D TCAD физической модели мажоритарного элемента. При моделировании сбора заряда с треков одиночных ионизирующих частиц используются NМОП и PМОП транзисторы элемента D1 и транзисторы N4.1, P4.1 элемента D4. Для наглядности восприятия 3D кремниевых приборных областей структуры на рис. 1б убрано объемное изображение мелкой траншейной оксидной изоляции (Shallow Trench Isolation – STI), охватывающей до глубины 400 нм кремниевые области транзисторов. На левой грани приборной части модели на рис. 1б отмечено значение глубины 650 нм, соответствующей нижней границе слоев переноса (диффузии) генерируемых на треке неосновных носителей заряда. Высоколегированные области с обозначениями n+ и p+ на рис. 1б являются элементами защитных колец. На рис. 1б показаны два трека частиц с направлениями по нормали к поверхности приборной физической модели в область NМОП транзисторов – трек TN(0) и в область PМОП транзисторов – трек TP(0), которые используются при моделировании. Треки с точками входа в области групп транзисторов обозначаются как TN(0) и TP(0), а треки с точками входа в мелкую траншейную изоляцию как TN(dT) и TP(dT), где dT – расстояние от точки входа трека до границы области группы транзисторов, собирающих заряд неосновных носителей с этого трека (рис. 2). При 3D TCAD моделировании использованы физические модели транзисторов [8] по проектной норме 65-нм КМОП объемной технологии. Энергетическая составляющая генерации заряда на треке характеризуется [9] линейной передачей энергии частицей на трек (linear energy transfer – LET).

2.2. Эскиз топологии элемента. Особенности расположения точек входов треков. Эскиз топологии мажоритарного элемента приведен на рис. 2. Транзисторы одного типа проводимости элементов D1, D2, D3 расположены в отдельных областях кремния, ограниченных на рис. 2 прямоугольниками. Эти области окружены мелкой траншейной изоляцией диоксидом кремния до глубины 400 нм, полоски с штриховкой обозначают затворы транзисторов, ширина каналов NМОП и PМОП транзисторов составляет 400 нм. Группы из трех транзисторов, выполнены в областях кремния размером 885 × 400 нм, группы из двух транзисторов в областях кремния размером 590 × 400 нм. Транзисторы N4.1и N4.2 элемента D4 по причине обеспечения необходимой логической функции исследуемого элемента выполнены в отдельных областях кремния размером 360 × 400 нм (рис. 2).

Точки входов треков одиночных частиц отмечены на рис. 2 звездочками. При моделировании использованы точки входа трека непосредственно в области кремния двух приборных областей расположены транзисторов: первой трек TN(0) с NМОП транзисторами N1.1, N1.2 и второй трек TP(0) с PМОП транзисторами P1.1, P1.2 элемента D1 и транзистором P4.1 элемента D4. Кроме того, использованы точки входа трека в слой мелкой траншейной оксидной изоляции на расстояниях dТ = 40 нм и с 100 до 700 нм (с шагом 100 нм) до каждой из этих двух приборных областей кремния: до первой с транзисторами N1.1, N1.2 и второй с транзисторами P1.1, P1.2 и P4.1. Значения емкости узла выхода первого элемента 2И-НЕ D1 (с учетом нагрузки входом элемента D4) равна 1.2 фФ, а емкость узла выхода элемента 3И-НЕ D4 (без нагрузки) равна 0.6 фФ.

3. ОСОБЕННОСТИ ОБРАЗОВАНИЯ ИМПУЛЬСА ТОКА ЧЕРЕЗ PN ПЕРЕХОД СТОКА ТРАНЗИСТОРА, СОБИРАЮЩИЙ ЗАРЯД С ТРЕКА ОДИНОЧНОЙ ЧАСТИЦЫ

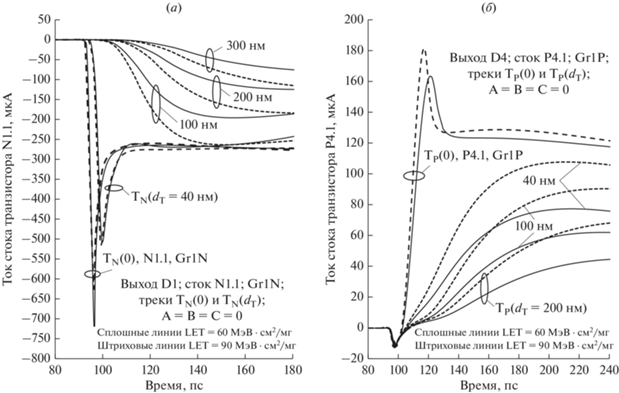

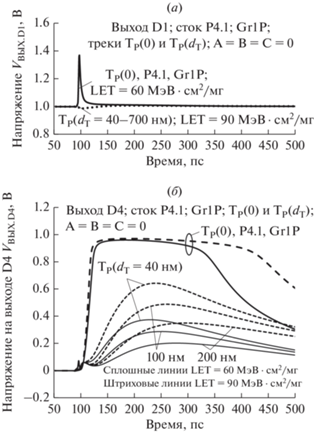

3.1. Импульсы тока при сборе NМОП транзисторами заряда электронов с треков. Узел выхода элемента 2И-НЕ D1 объединяет транзисторы двух групп Gr1N и Gr1P (рис. 1 и 2), а именно стоки NМОП транзистора N1.1, стоки PМОП транзисторов P1.1, P1.2, а также затвор PМОП транзистора P4.1 элемента 3И-НЕ D4. Образование импульсов тока NМОП транзисторами N1.1, N1.2 при сборе заряда с треков TN(0) и TN(dT) происходит при сигналах на входах элемента А = B = C = 0 (рис. 3а), когда NМОП транзисторы N1.1, N1.2 заперты. Соответствующие зависимости при LET = 60 или 90 МэВ · см2/мг приведены на рис. 3а.

Рис. 3.

Импульсы тока через стоки транзистора N1.1 элемента D1 и транзистора P4.1 элемента D4 с точками входа трека TN(0) в группу транзисторов Gr1N и трека TP(0) в группу транзисторов Gr1N, а также треков TN(dТ) и TP(dТ) с точками входа в слой мелкой траншейной изоляции на расстояниях dТ = 40, 100, 200 и 300 нм от края области группы транзисторов, собирающих заряд; на входах сигналы А = B = C = 0; момент времени образования трека 92–100 пс; LET = 60 и 90 МэВ · см2/мг: (а) импульсы через сток транзистора N1.1 на выходе элемента D1; (б) импульсы через сток транзистора P4.1 на выходе элемента D4.

При треках с точками входа TN(0) непосредственно в область Gr1N (рис. 2) транзисторов N1.1, N1.2, а также в область слоя изоляции TN(dТ = = 40 нм) происходит за время 3–3.5 пс переход узла выхода элемента 2И-НЕ D1 (сток N1.1) из состояния с напряжением VВЫХ.D1 = 1 В в в инверсное смещение транзисторов N1.1, N1.2 (рис. 3а) с напряжением на стоке транзистора N1.1 VВЫХ.D1 = = –0.65–0.4 В. Такое переключение формирует импульсы тока с амплитудными “выбросами” на фронтах отрицательной полярности –730–515 мкА сбором заряда 1.24–1.27 фКл при переносе энергии на треки LET = 60 или 90 МэВ · см2/мг. После такого “начального” сбора заряда происходит ограничение выноса заряда током около 260 мкА на время до 250 пс при треке TN(0) и на время 50 пс при треке TN(dТ = 40 нм) в слой диэлектрика. Далее следует экспоненциальный спад токов импульсов с постоянными времени τСПАД = 100–150 пс (рис. 3а). Импульсы тока при точках входа треков с dТ ≥ 100 нм не имеют начального “выброса” и характеризуются (рис. 3а) во времени зависимостью, близкой к двухэкспоненциальной [10, 11].

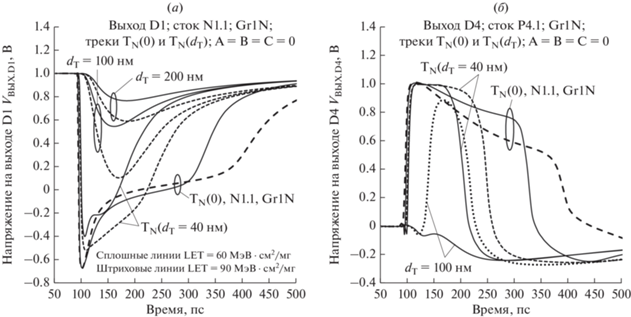

3.2. Импульсы напряжения при сборе NМОП транзисторами заряда электронов с треков. Импульсы напряжения на узле выхода элемента D1 (стоковый pn переход транзистора N1.1) образуются при сборе заряда электронов с треков TN(0) (рис. 3а) и TN(dТ) при сигналах на входах исследуемого элемента А = B = C = 0, когда транзисторы N1.1; N1.2, собирающие заряд в группе Gr1N, заперты и, заряжая емкость узла, формируют на нем импульсы с амплитудой более 1 В (см. рис. 4а и табл. 1). Импульсы напряжения на выходе D1 при TN(0) имеют практически трапециидальную форму, а при треке TN(dТ) с dТ = 40 нм имеют треугольную форму (рис. 4а). Изменение напряжения на выходе элемента D1 инвертируется транзисторами P4.1 и N4.1 элемента D4, что образует на узле выхода элемента D4 импульс помехи положительной полярности (рис. 4б) длительностью около 200 пс при сборе заряда с трека TN(0) в область Gr1N и длительностью 100–140 пс при треке TN(dТ), с точкой входа на расстоянии dТ = 40 нм при LET = 60 и 90 МэВ × см2/мг. При точке входа трека с dТ = 100 нм импульс помехи на выходе D4 с длительностью 50 пс образуется только при LET = 90 МэВ · см2/мг. При точках входа трека с расстоянием dТ ≥ 100 нм амплитуды импульсов на выходе элемента D1 снижаются меньше порога запирания транзистора N4.1, что сохраняет на выходе D4 уровень логического нуля “0” без образования помех (рис. 4б).

Рис. 4.

Импульсы напряжения на узлах выходов элементов D1 и D4 при треках с точкой входа трека TN(0) в группу транзисторов Gr1N (N1.1 и N1.2) и треков TN(dТ) с точками входа на расстояниях dТ = 40, 100 и 200 нм от края области NМОП транзисторов Gr1N, собирающих заряд; на входах элемента сигналы А = B = C = 0; момент времени образования трека 100 пс; LET = 60 и 90 МэВ · см2/мг: (а) импульсы на выходе элемента D1; (б) импульсы на узле выхода элемента D4, образовавшиеся при передаче импульсов с выхода D1 VВЫХ.D1 через инвертор на транзисторах P4.1 и N4.1.

Таблица 1.

Параметры импульсов тока и напряжения, образованных сбором заряда с треков одиночных частиц с точками входа трека TN(0) и TP(0) в приборные области кремния, а также треков TN(dT) и TP(dT) с точками входа в изолирующий диэлектрик на расстоянии dT = 40 нм до границ приборных областей

| Входные сигналы | A = B = C = 0 | A = B = C = 1 | A = B = C = 0 | |||

|---|---|---|---|---|---|---|

| Трек частицы | TN(0) и TN (dT = 40 нм) | TP(0) и TP (dT = 40 нм) | TP(0) и TP (dT = 40 нм) | |||

| Узлы и транзисторы, собирающие заряд | Узел D1; N1.1; N1.2 | Узел D1; P1.1; P1.2 | Узел D4; P4.1 | |||

| LET, МэВ ≥ см2/мг | 60 | 90 | 60 | 90 | 60 | 90 |

| IМАКС, мкА | 730 (505) | 625 (515) | 585 (260) | 380 (315) | 163 (77) | 182 (110) |

| tl.МАКС, пс | 3.5 (5) | 3.5 (4.3) | 4.2 (5.8) | 5.1 (4.8) | 28.5 (115) | 14 (115) |

| QПЕРЕКЛ, фКл | 1.27 (1.25) | 1.24 (1.1) | 1.23 (1.4) | 0.97 (1.55) | 1.5 (4.45) | 1.35 (6.20) |

| VМАКС, В | 1.2 (1.2) | 1.2 (0.8) | 0.9 (0.5) | 1.2 (0.85) | 0.96 (0.37) | 0.97 (0.65) |

| tV.МАКС, пс | 3.5 (8) | 3.5 (10) | 1.0 (8) | 2.0 (9) | 183 (135) | 190 (145) |

Примечание: 1) в скобках приведены параметры импульсов тока и напряжения при точках входа треков в изолирующий диэлектрик на расстоянии dT = 40 нм до границ приборных областей кремния; 2) амплитудные значения импульсов напряжения VМАКС для треков TN(0) и TN(dТ) с dТ = 40 нм узла D1 усреднены в интервалах 250 и 100 пс соответственно, после возникновения треков.

3.3. Импульсы тока при сборе PМОП транзисторами заряда дырок с треков. PМОП транзисторы P1.1, P1.2 группы Gr1P, соединенные стоками с узлом выхода D1, заперты при входных сигналах А = B = C = 1 и могут собирать заряды с треков TN(0) и TN(dТ), в то время как транзистор P4.1, расположенный в той же группе Gr1P, при А = B = C = = 1 открыт и не собирает. PМОП транзистор P4.1 заперт и собирает заряд при А = B = C = 0, когда открыты транзисторы P1.1, P1.2. Параметры импульсов тока и напряжения на узлах D1 и D4 приведены в табл. 1.

Примеры импульсов тока при сборе заряда с треков TP(0) и TP(dТ) одним PМОП транзистором P4.1 является сбор заряда при сигналах на входах элемента А = B = C = 0 (рис. 3б), а соответствующие им примеры импульсов напряжения при сборе заряда приведены на рис. 5. Результатом сбора заряда является образование импульсов на узле выхода элемента D4. Сбор заряда величиной 1.35–1.5 фКл запертым транзистором P4.1 при образовании трека с точкой входа в кремниевую область Gr1P или трека TP(dТ) при dТ = 40 нм (рис. 2) приводит к переходу за время 1.35–1.5 пс при LET = = 60 и 90 МэВ · см2/мг выходного узла элемента D4 из состояния с напряжением VВЫХ.D4 = 0 В в состояние с напряжением VВЫХ.D4 = 0.96–0.98 В (см. табл. 1). Такое переключение формирует импульсы тока с амплитудными “выбросами” на фронтах положительной полярности со значениями 163–182 мкА (рис. 3б) при переносе энергии LET = 60 или 90 МэВ · см2/мг.

Рис. 5.

Импульсы напряжения на узлах выходов элементов D1 и D4 при сборе заряда транзистором P4.1 с трека TP(0) в группу Gr1P, а также при сборе заряда с треков TP(dТ) с точками входа на расстояниях dТ = 40, 100 и 200 нм от края области транзисторов группы Gr1P (P1.1, P1.2 и P4.1), на входах исследуемого элемента А = B = C = 0; LET = 60 и 90 МэВ · см2/мг: (а) импульсы на выходе элемента D1; (б) импульсы на выходе элемента D4.

После такого “начального” сбора заряда происходит ограничение выноса заряда током 120–128 мкА на время до 200 пс при точке входа трека в группу транзисторов Gr1P при LET = 60 МэВ · см2/мг и на время 300 пс при LET = 90 МэВ · см2/мг. Далее следует экспоненциальный спад импульсов тока, характеризуемый постоянными времени τСПАД = 270–380 пс.

3.4. Импульсы напряжения при сборе PМОП транзисторами заряда дырок с треков. При сигналах на входах исследуемого элемента. А = B = C = = 0 транзисторы P1.1, P1.2 в группе Gr1P открыты, транзистор P4.1 узла D4 заперт и, собирая заряд, формирует импульсы положительной полярности на емкости выхода элемента D4 (рис. 5б) с амплитудой 0.96 В и длительностью 245 пс при LET = 60 МэВ · см2/мг или с амплитудой 0.97 В и длительностью 350 пс при LET = 90 МэВ · см2/мг. При этом па узле выхода D1 сохраняется напряжение VВЫХ.D1 = 1 В (рис. 5а). При точке входа трека на расстоянии dТ = 40 нм от края области Gr1P (рис. 5б) импульсы напряжения не превышают 0.4 и 0.65 В соответственно при LET = = 60 и 90 МэВ · см2/мг.

4. ОСНОВНЫЕ РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ

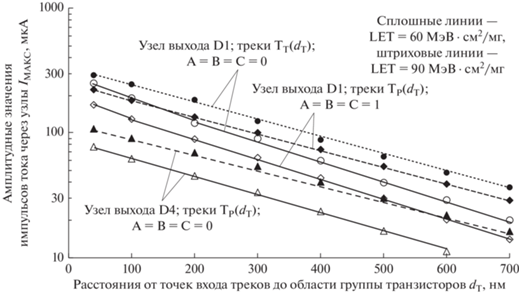

4.1. Амплитудные значения импульсов тока через узлы выходов элементов D1 и D4 в зависимости от расстояния точки входа трека до приборных областей групп транзисторов Gr1N и Gr1P. Амплитудные значения импульсов тока при сборе заряда с треков одиночных частиц в зависимости от расстояния от точки входа трека до границы области кремния с транзисторами, собирающими заряд, приведены на рис. 6. При моделировании использованы треки с точками входа на расстояниях dТ от 40 до 700 нм до областей кремния с NМОП транзисторами группы Gr1N (рис. 3а) и PМОП транзисторами группы Gr1P (рис. 3б). При точках входа трека в слой траншейной оксидной изоляции на малом расстоянии dТ = 40 нм от края приборной области, то при сборе заряда NМОП транзисторами (рис. 3а) происходит переключение NМОП транзисторов в инверсный режим смещения. Если заряд собирают PМОП транзисторы, то перехода в инверсный режим смещения практически нет, поскольку в этом состоянии PМОП транзистор оказывается не более 10 пс.

Рис. 6.

Амплитудные значения импульсов тока через стоки транзистора N1.1 элемента D1, P4.1 элемента D4 и транзисторов P1.1, P1.2 элемента D1 в зависимости от расстояний точек входов треков dТ в слой мелкой траншейной изоляции до приборных областей групп транзисторов при треках TN(dТ) в группу NМОП транзисторов Gr1N и TP(dТ) в группу PМОП транзисторов Gr1P при LET = 60 и 90 МэВ ⋅ см2/мг.

Для точек входа трека, начиная с расстояния dТ = 100 нм при сборе заряда транзисторами зависимости на рис. 6 описываются экспоненциальными функциями вида 10–dТ/Δd0.1 = exp(–2.3dТ/Δd0.1), что отображается прямыми линиями при логарифмической шкале максимумов токов импульсов тока IМАКС. Снижение амплитуд импульсов тока в 10 раз при увеличении расстояния точки входа трека dТ для всех зависимостей на рис. 6 характеризуют практически одинаковые значения коэффициентов наклона Δd0.1 = 680–730 нм. Эти значения эквивалентны снижению амплитудных значений импульсов тока в 1.8–2.0 раза при увеличении на 200 нм расстояния от точки входа трека до области транзисторов, собирающих заряд.

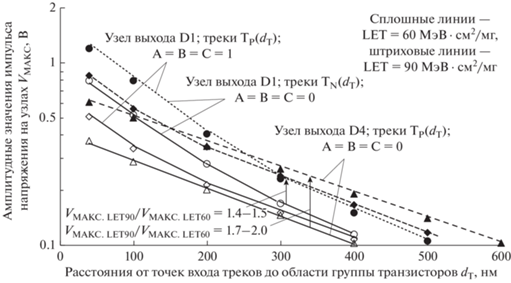

4.2. Амплитудные значения импульсов напряжения на узлах выходов элементов D1 и D4. 4.2.1. Зависимости от расстояния точки входа трека до областей групп транзисторов. Амплитудные значения импульсов напряжения при сборе заряда с треков одиночных частиц в зависимости от расстояния от точки входа трека до границы области кремния с транзисторами, собирающими заряд, приведены на рис. 7.

Рис. 7.

Амплитудные значения импульсов напряжения на емкостях узлов выходов элементов D1 и D4 в зависимости от расстояний точек входов треков dТ в слой мелкой траншейной изоляции до приборных областей групп транзисторов при треках TN(dТ) в группу NМОП транзисторов Gr1N и TP(dТ) в группу PМОП транзисторов Gr1P при LET = 60 и 90 МэВ ⋅ см2/мг.

Результаты моделирования даны точками с маркерами на рис. 7 шести зависимостей VМАКС(dТ), которые характеризуют изменение амплитудных значений импульсов на выходе элемента D1 при сборе заряда NМОП транзисторами группы Gr1N при сигналах на входах исследуемого элемента А = B = C = 0 или PМОП транзисторами группы Gr1P элемента D1 при А = B = C = 1, а также на выходе элемента D4 при сборе заряда в группе Gr1P PМОП транзистором P4.1 элемента D4 при А = B = C = 0. Эти три вида зависимостей приведены в двух вариантах: сплошными линиями на рис. 7 даны зависимости при LET = 60 МэВ · см2/мг, штриховыми линиями при LET = 90 МэВ · см2/мг. Зависимости, обусловленные сбором заряда как NМОП, так и PМОП транзисторами сгруппировались в два семейства: одно при LET = 60 МэВ · см2/мг, а второе при LET = 90 МэВ · см2/мг (рис. 7).

Из сопоставления зависимостей на рис. 7 следует, что максимумы значений импульсов при сборе электронов NМОП транзисторами N1.1, N1.2 элемента D1 с треков с линейным переносом энергии на них LET = 90 МэВ · см2/мг больше в 1.4–1.5 раза, чем для треков с LET = 60 МэВ · см2/мг для тех же точек входа трека. При сборе дырок PМОП транзисторами P1.1, P1.2 элемента D1 или P4.1 элемента D4 с треков с LET = 90 МэВ · см2/мг максимумы импульсов больше в 1.7–2.0 раза, чем для треков с LET = 60 МэВ · см2/мг. Эти результаты удовлетворительно согласуются с увеличением переноса энергии (LET) частицами на треки в 1.5 раза.

Для точек входа трека, начиная с расстояния dТ = 100 нм при сборе заряда дырок PМОП транзисторами и dТ = 200 нм при сборе заряда электронов NМОП транзисторами, группы зависимостей на рис. 7 являются экспоненциальными функциями вида exp(–2.3dТ/Δd0.1), что отображается прямыми линиями при логарифмической шкале значений VМАКС. Снижение максимумов импульсов в 10 раз при увеличении расстояния точки входа трека dТ характеризуют коэффициенты наклона зависимостей Δd0.1 = 500–600 нм для семейства зависимостей NМОП транзисторов при LET = 60 МэВ · см2/мг и Δd0.1 = 650–750 нм для зависимостей PМОП транзисторов при LET = = 90 МэВ · см2/мг (рис. 7).

При перемещении точки входа трека из области кремния в область оксида кремния происходит более резкое снижение амплитуд импульсов для треков, с которых собираются дырки, по сравнению с треками, с которых собираются электроны (рис. 7). Также в переходной области заметнее снижаются максимальные значения импульсов для треков с LET = 60 МэВ · см2/мг, чем для треков с LET = 90 МэВ · см2/мг.

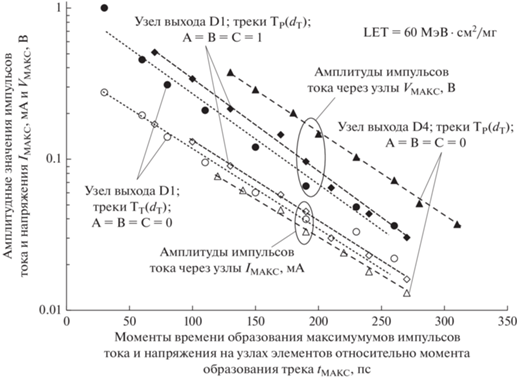

4.2.2. Зависимости как функции моментов времени достижения амплитудных значений. Амплитудные значения импульсов напряжения на выходах элементов D1 и D4 как функции момента времени достижения амплитудных значений импульса напряжения tМАКС относительно момента образования трека при треках с LET = 60 и 90 МэВ · см2/мг приведены на рис. 8. Момент времени достижения максимального значения импульсом напряжения VМАКС, образованного зарядом емкости узла D1 импульсом тока, сформированным сбором неосновных носителей заряда, практически совпадает с значением момента времени максимального значения соответствующего импульса тока IМАКС, находясь в том же интервале 10 пс, что и максимум амплитуды тока IМАКС. На узле D4 момент времени максимального значения импульса напряжения VМАКС характеризуется дополнительной задержкой 10 пс (рис. 8) поскольку импульс передается с узла D1 на узел D4 инвертором на транзисторах P4.1 и N4.1 (см. рис. 1а).

Рис. 8.

Амплитудные значения импульсов тока и напряжения, образующиеся при сборе заряда выходным узлом элемента D1, как функции одновременного образования максимумов этих импульсов tМАКС для точек входов треков TN(dТ) и TP(dТ) с расстояниями от 40 до 700 нм до краев приборных областей кремния Gr1N и Gr1P при LET = = 60 МэВ · см2/мг, а также при сборе заряда выходным узлом элемента D4 через сток транзистора P4.1 с образованием максимумов импульсов напряжения с задержкой 10 пс относительно максимумов импульсов тока для точек входов треков TP(dТ) в слой мелкой траншейной изоляции группы PМОП транзисторов Gr1P при LET = 60 МэВ · см2/мг. Сплошные маркеры соответствуют амплитудам импульсов напряжения VМАКС, а маркеры только с контурными линиями, но с теми же, что у сплошых, соответствуют амплитудам импульсов тока IМАКС, в частности, и при том же значении tМАКС.

Оценки длительностей сбора заряда по значениям tСБОР = tМАКС лежат в диапазоне до 340 пс, возрастая при увеличении расстояния до точки входа трека dТ и синхронном экспоненциальном снижении максимального значения импульса напряжения VМАКС на выходах D1 и D4 для трех видов зависимостей в двух вариантах каждая: сплошными линиями на рис. 8 даны зависимости при LET = 60 МэВ · см2/мг и штриховыми линиями при LET = 90 МэВ · см2/мг. Коэффициенты снижения максимальных значений импульсов напряжения в 10 раз при увеличении момента времени достижения максимума импульса напряжения tМАКС для логарифмической шкалы зависимостей на рис. 8 имеют значения Δt0.1 = 180–200 пс. При LET = 60 и 90 МэВ · см2/мг амплитудные значения импульсов напряжения на узле выхода D1, выводящем заряд двумя NМОП или двумя PМОП транзисторами в диапазоне точек входа трека от 40 до 200 нм могут снижаться в 1.5–2.0 раза (см. рис. 7) при увеличении расстояиия точки входа трека на 100 нм.

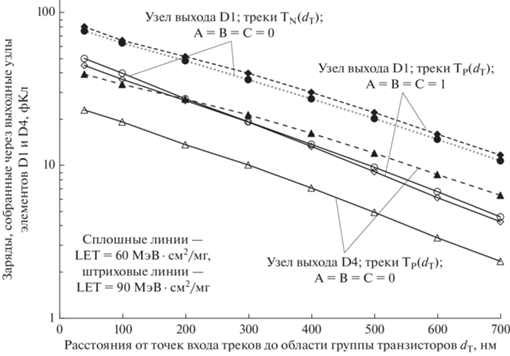

4.3. Зависимости значений зарядов, перенесенных импульсами тока в узлы выходов элементов D1 и D4 от расстояния точки входа трека dТ до приборных областей групп транзисторов Gr1N и Gr1P. Значения величин зарядов, перенесенных импульсами тока в узлы выходов элементов И-НЕ D1 и D4 в зависимости от расстояния точки входа трека до границы области кремния с транзисторами, собирающими заряд, приведены на рис. 9. При моделировании использованы треки с точками входа в слой траншейной оксидной изоляции на расстояниях dТ от 40 до 700 нм до областей кремния с NМОП транзисторами группы Gr1N и PМОП транзисторами группы Gr1P.

Рис. 9.

Значения величин зарядов, выведенных (собранных) через выходные узлы элементов D1 и D4, в зависимости от расстояния точки входа dТ треков TN(dТ) и TP(dТ) в слой мелкой траншейной изоляции до кремниевой области транзисторов Gr1N и Gr1P в диапазоне dТ = 40–700 нм при LET = 60 и 90 МэВ · см2/мг.

Для точек входа трека, начиная с расстояния dТ = = 40 нм, зависимости сбора заряда транзисторами выходными узлами элементов 2И-НЕ и 3И-НЕ описываются экспоненциальными функциями 10–dТ/Δd0.1 = exp(–2.3dТ/Δd0.1), что отображается практически линейными зависимостями при логарифмической шкале зарядов как функций от расстояния точки входа трека в слой траншейной оксидной изоляции. Снижение собранного заряда в 10 раз при увеличении расстояния точки входа трека dТ характеризуют коэффициенты наклона в диапазоне Δd0.1 = 680–780 нм собирающих заряд узлов как NМОП, так и PМОП транзисторами (рис. 9). Это соответствует снижению собранного заряда вдвое при увеличении расстояния точки входа трека на каждые 200 нм от области транзисторов, собирающих заряд с трека (см. данные в табл. 2).

Таблица 2.

Заряды QВЫХ.D1, QВЫХ.D4 (фКл), собранные КМОП транзисторами через узлы исследуемого элемента в зависимости от расстояния точки входа трека dT (нм) треков TN(dТ) и TP(dТ) до границ областей групп транзисторов Gr1N и Gr1P, собирающих заряд с этих трека при LET = 60 и 90 МэВ · см2/мг

| dT, нм | QВЫХ.D1, фКл | QВЫХ.D1, фКл | QВЫХ.D4, фКл | |||

|---|---|---|---|---|---|---|

| Gr1N, A = B = C = 0 | Gr1P, A = B = C = 1 | Gr1P, A = B = C = 0 | ||||

| 60 МэВ ⋅ см2/мг | 90 МэВ ⋅ см2/мг | 60 МэВ ⋅ см2/мг | 90 МэВ ⋅ см2/мг | 60 МэВ ⋅ см2/мг | 90 МэВ ⋅ см2/мг | |

| 0 | 80 | 109 | 78 | 105 | 42 | 55 |

| 40 | 53 | 76 | 50 | 81 | 22 | 40 |

| 100 | 38 | 63 | 37 | 66 | 18 | 34 |

| 200 | 28 | 48 | 26 | 51 | 14 | 27 |

| 300 | 19 | 36 | 19 | 40 | 10 | 21 |

| 400 | 14 | 27 | 13 | 30 | 7 | 16 |

| 500 | 10 | 20 | 9 | 22 | 5 | 11 |

| 600 | 7 | 15 | 6 | 16 | 3 | 9 |

| 700 | 5 | 11 | 4 | 12 | 2 | 6 |

Величины зарядов, перенесенных импульсами тока с расстояний dТ = 40–700 нм при сборе заряда группами Gr1N и Gr1P как из двух NМОП транзисторов, так и двух PМОП транзисторов одного общего узла элемента 2И-НЕ D1, составляет от 50–53 до 4–5 фКл при LET = 60 МэВ · см2/мг и от 81–76 до 11–11 фКл при LET = 90 МэВ · см2/мг. Величины зарядов, перенесенных при сборе заряда одним PМОП транзистором P4.1, составляет от 22 до 2 фКл при LET = = 60 МэВ · см2/мг и от 40 до 6 фКл при LET = = 90 МэВ · см2/мг.

Импульсы ошибок на выходе моделируемого мажоритарного элемента с амплитудой 0.7–1 В образуются при точках входа трека непосредственно в область приборного кремния NМОП и PМОП транзисторов, а также при треках с точками входа в слой траншейной изоляции на расстояниях 40–100 нм от границы областей приборного кремния преимущественно при сборе заряда NМОП транзисторами.

ЗАКЛЮЧЕНИЕ

Надежность микропроцессорных высокопроизводительных вычислительных систем космического применения зависит, в частности, от повышения устойчивости логических элементов к воздействиям одиночных ионизирующих частиц. Полученные в данной работе результаты будут полезны при выборе расположения контактов, выводящих из кристалла микросхемы заряды, образованные в кремнии под слоем мелкой траншейной изоляции. Это нужно для минимизации одновременного сбора заряда несколькими транзисторами с одного трека, снижения длительности импульсных помех на выходах логических элементов и, соответственно, повышения надежности защиты активных элементов от воздействий одиночных ионизирующих частиц.

Список литературы

Johnston A.H., Swimm R.T., Allen G.R., Miyahira T.F. Total Dose Effects in CMOS Trench Isolation Regions // IEEE Transactions on Nuclear Science. 2009. V. 56. № 4. P. 1941–1949.

Turowski M., Raman A., Schrimpf R.D. Nonuniform Total-Dose-Induced Charge Distribution in Shallow-Trench Isolation Oxides // IEEE Transactions on Nuclear Science. 2004. V. 51. № 6. P. 3166–3171.

Haghi M., Draper J. Comparison of Charge Sharing Reduction Techniques in Deep Sub-micron CMOS // 54th International Midwest Symposium on Circuits and Systems (MWSCAS). 2011. P. 1–4.

Tanaka K., Nakamura H., Uemura T., Takeuchi K., Fukuda T., Kumashiro S. Study on Influence of Device Structure Dimensions and Profiles on Charge Collection Current Causing SET Pulse Leading to Soft Errors in Logic Circuits // Proc. of IEEE International Conference on Simulation of Semiconductor Processes and Devices (ICSSPD). 2009. P. 1–4.

Катунин Ю.В., Стенин В.Я. Элемент совпадения на основе ячейки памяти STG DICE для ассоциативных запоминающих устройств, сбоеустойчивых к воздействиям одиночных ядерных частиц // Микроэлектроника. 2018. Т. 47. № 2. С. 158–174.

Katunin Yu.V., Stenin V.Ya. The STG DICE Cell with the Decoder for Reading Data in Steady and Unsteady States for Hardened SRAM // in IEEE Xplore (Conference Section, RADECS-2017), e-book, 2019. P. 171–178.

Стенин В.Я., Катунин Ю.В. КМОП мажоритарный элемент на основе И-НЕ логики с пониженной чувствительностью к воздействию одиночных ионизирующих частиц // Микроэлектроника. 2021. Т. 50. № 6. С. 435–444.

Garg R., Khatri S.P. Analysis and design of resilient VLSI circuits: mitigating soft errors and process variations. N.Y.: Springer, 2010. P. 194–205.

Soft errors in Modern Electronic Systems / Nicolaidis M., Ed. N.Y.: Springer, 2011. P. 27–54.

Messenger G. Collection of charge on junction nodes from ion tracks // IEEE Transactions on Nuclear Science. 1982. V. 29. № 4. P. 2024–2031.

Dodd P.E., Massengill L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics // IEEE Transactions on Nuclear Science. 2003. V. 50. № 3. P. 583–602.

Дополнительные материалы отсутствуют.

Инструменты

Микроэлектроника