Микроэлектроника, 2022, T. 51, № 6, стр. 423-428

Методика итерационного уточнения значений параметров в аналитических моделях микроэлектронных устройств на основе интегральных моп-транзисторов

А. С. Синюкин 1, *, А. В. Ковалев 1, **

1 Дизайн-центр микроэлектронной компонентной базы для систем искусственного интеллекта Южного федерального университета

347922 Ростовская область, Таганрог, ул. Шевченко, 2, корпус “К”, Россия

* E-mail: sinyukin@sfedu.ru

** E-mail: avkovalev@sfedu.ru

Поступила в редакцию 16.06.2022

После доработки 11.07.2022

Принята к публикации 11.07.2022

- EDN: ZDXSWP

- DOI: 10.31857/S0544126922700132

Аннотация

Физические модели МОП-транзисторов, применяемые при проектировании современных интегральных микросхем, характеризуются высокой точностью, что позволяет с заданной степенью достоверности моделировать их работу. Однако они также отличаются высокой сложностью, из-за чего их непрактично использовать при анализе и прогнозировании работы проектируемых устройств. Поэтому для оценивания и прогнозирования обычно применяются менее точные, но более компактные аналитические модели транзисторов и устройств на их основе. В то же время не всегда при расчетах и оценивании значения всех параметров, составляющих уравнения модели, могут быть известны с достаточной степенью точности. В статье, на примере разработанной ранее аналитической модели умножителя напряжения и результатов моделирования разработанного по технологии КМОП 180 нм умножителя напряжения, представлена методика уточнения значений параметров аналитических моделей, описывающих устройства на основе интегральных МОП-транзисторов.

1. ВВЕДЕНИЕ

На сегодняшний день МОП-транзисторы являются одними из ключевых компонентов, на основе которых строятся аналоговые, цифровые и аналого-цифровые микроэлектронные устройства. Особенно велика роль МОП-транзисторов при проектировании интегральных микросхем, в связи с чем существует потребность в точном и достоверном воспроизведении их физических, конструктивных, технологических и схемотехнических особенностей. С этой целью разработаны высокоточные физические модели МОП-транзисторов, например MOS9, BSIM3, BSIM4 [1] и другие. Такие модели могут включать сотни уравнений, содержащих тысячи параметров, ввиду чего они позволяют описывать и моделировать устройства на основе МОП-транзисторов с высокой степенью точности, сопоставимой с результатами измерения экспериментальных образцов. Для выполнения подобного моделирования применяются сложные САПР, например от компаний Synopsys, Mentor Graphics и Cadence [2]. В свою очередь достоверные значения ряда параметров для этих моделей устанавливаются в процессе итерационного экстрагирования параметров путем исследования нескольких изготовленных образцов транзисторов разных размеров. Следствием такого комплексного подхода оказывается высокая сложность моделей, в результате чего они малоприменимы для аналитических расчетов и прогнозирования.

При разработке микроэлектронных устройств, особенно на ранних стадиях проектирования, для прогнозирования их работы и оценки параметров во многих случаях удобнее пользоваться более компактными аналитическими моделями. Однако и в этом случае чем точнее будут выбраны значения параметров при оценочных расчетах, тем меньшей будет погрешность результатов этих расчетов по сравнению с результатами измерения или высокоточного моделирования. С целью снижения погрешности, возникающей при аналитических расчетах, предлагается методика уточнения или определения неизвестных значений параметров компактных аналитических моделей, характеризующих микроэлектронные устройства на основе интегральных МОП-транзисторов.

2. МЕТОДИКА УТОЧНЕНИЯ ЗНАЧЕНИЙ ПАРАМЕТРОВ АНАЛИТИЧЕСКИХ МОДЕЛЕЙ

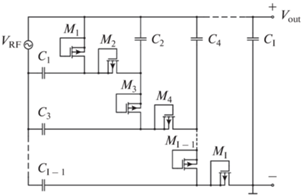

Методика рассматривается на примере разработанных ранее моделей многокаскадных умножителей напряжения [3, 4], в основу которых были положены модель наноразмерных транзисторов EKV [5] и модель умножителя Диксона [6]. Умножители напряжения широко применяются в качестве компонента источников питания в беспроводных пассивных (безбатарейных) микроустройствах, которые используются в сетях беспроводных датчиков [7–9], в приложениях интернета вещей [10–12] и радиочастотной идентификации [13–15], при мониторинге целостности конструкций [16, 17] и в других областях. В модифицированной схеме умножителя (рис. 1) выводы подложки p-канальных МОП-транзисторов в диодном включении соединены с выводами затворов и стоков этих транзисторов, благодаря чему значительно снижается негативное влияние эффекта подложки на характеристики транзисторов. В результате этого значение тока транзисторов и падения напряжения на транзисторах остается приблизительно постоянным независимо от числа каскадов.

К особенностям используемых моделей умножителя можно отнести то, что они, во-первых, описывают работу устройства в режимах, соответствующих областям слабой и сильной инверсии МОП-транзисторов, а во-вторых, учитывают реальные падения напряжения на транзисторах в диодном включении при увеличении числа умножающих каскадов. Модели содержат выражения для определения напряжения на выходах контуров умножителя (каждый каскад включает в себя два контура, то есть N = 2I, рис. 1), тока транзисторов в диодном включении и падения напряжения на этих транзисторах. Выражения модели, характеризующей работу умножителя в области слабой инверсии МОП-транзистора, записываются следующим образом [3]:

(2)

${{I}_{d}} = {{I}_{0}}{\kern 1pt} {\text{exp}}\left( {\frac{{n{{V}_{d}} - {{V}_{{T0}}}}}{{n{{\varphi }_{T}}}}} \right),$(3)

${{V}_{d}} = {{\varphi }_{T}}{\kern 1pt} {\text{ln}}{\kern 1pt} \frac{{{{I}_{d}}}}{{{{I}_{0}}}} + \frac{{{{V}_{{T0}}}}}{n},$Выражения модели, характеризующей работу в области сильной инверсии, запишутся следующим образом [3]:

(4)

${{V}_{{i + 1}}} = {{V}_{i}} + \frac{C}{{C + {{C}_{S}}}}{{V}_{a}} - {{V}_{d}} - \frac{{{{I}_{d}}}}{{f\left( {C + {{C}_{S}}} \right)}},$Согласно предлагаемой методике для уточнения значений параметров в аналитических моделях многокаскадных умножителей напряжения в первую очередь необходимо осуществить измерение или высокоточное моделирование искомого умножителя для получения значений напряжений на выходах каждого каскада, которые принимаются за истинные. В работе такое моделирование осуществлялось для построенного по КМОП-технологии TSMC 180 нм восьмикаскадного умножителя напряжения в программных модулях Virtuoso ADE и Spectre в составе САПР Cadence. Моделирование выполнялось с использованием моделей BSIM4 с учетом паразитных элементов, экстрагированных из топологии умножителя посредством САПР Calibre Interactive.

Методика применяется, если значение одного из параметров модели неизвестно, либо известно с недостаточной степенью точности. В этом случае используется известное или предполагаемое значение уточняемого параметра, и осуществляется расчет по выражениям (1)–(3) или (4)–(6) с использованием известных параметров. Выражения (1)–(3) применяются при амплитуде входных напряжений ниже порогового напряжения (Va < VT0), а выражения (4)–(6) – при амплитуде входных напряжений выше порогового (Va > VT0). Результат расчета – значения напряжений на выходах умножающих каскадов – сравнивается с результатом высокоточного моделирования (измерения).

В зависимости от результата сравнения либо значение уточняемого параметра принимается за корректное, либо осуществляется изменение значения уточняемого параметра и повторение расчета. Таким образом, процесс уточнения является итерационным и продолжается до тех пор, пока соответствие результатов расчета и результатов моделирования (истинных результатов) не достигнет заданной точности. При осуществлении итерационных процессов применяются хорошо отработанные методы оптимизации, которые позволяют избежать расходимости процессов и промахов [18]. Критерием точности соответствия результатов A является сумма разностей Δn между значениями напряжений на выходах каждого каскада для истинного и расчетного значений (сумма отклонений расчетных значений Vn,calc от значений Vn,sim, полученных из моделирования):

Сумма разностей A в идеальном случае стремится к нулю, а на практике должна достигать какого-то установленного значения, соответствующего точности определения интересуемого параметра. При осуществлении итерационного уточнения параметров важно, чтобы значения остальных параметров были известны с необходимой степенью точности. Рассматриваемая методика может применяться и для многофакторного уточнения, когда нужно определять значение более одного параметра – в этом случае используются методы многофакторной оптимизации [18].

3. РЕАЛИЗАЦИЯ МЕТОДИКИ УТОЧНЕНИЯ ПАРАМЕТРОВ

Для примера рассмотрим уточнение до единиц нА значения тока Id транзисторов в диодном включении при работе в области слабой инверсии. В данном случае параметры, составляющие выражения (1)–(6), можно разделить на следующие категории:

а) параметры, значения которых известны из схемы и топологии: ширина канала транзистора (W = 8.75 мкм), длина канала транзистора (L = = 250 нм), емкость конденсаторов (емкость единичного конденсатора, С = 500 фФ), паразитная емкость СS = 26.32 фФ;

б) параметры, значения которых известны из технологической документации: пороговое напряжение VT0 = 0.262 В, параметр наклона n = 1.497, подвижность носителей заряда μ = 0.025 м2/В с, удельная емкость затвор-канал Сox = 8.5 × 10–3 Ф/м2; дрейфовая скорость насыщения ${{v}_{{{\text{sat}}}}}$ = 8 × 104 м/с.

в) задаваемые параметры: амплитуда входного напряжения Va = 0.2 В (<VT0), частота входного сигнала f = 2.45 ГГц;

г) уточняемый параметр: значение тока транзисторов Id, соответствующее току, протекающему в умножителе напряжения;

д) рассчитываемые параметры: характеристический ток I0, технологический коэффициент K.

Значения характеристического тока I0 рассчитывалось по выражению [19]:

При моделировании устанавливались следующие значения параметров: Va = 0.2 В (<VT0); f = = 2.45 ГГц; сопротивление нагрузки R = 100 МОм.

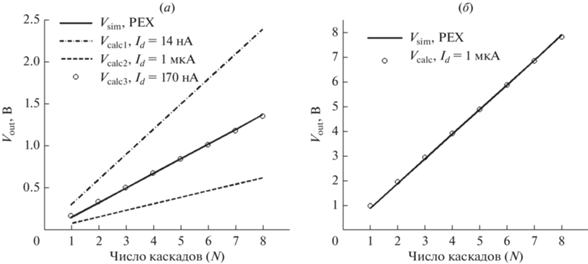

В первой итерации значение тока Id было принято за 14 нА (исходя из приближенной оценки: Id = Vout/R = 1.3679 В/100 МОм ≈ 14 нА). При этом значение критерия A составило 4.6853 В, что соответствует усредненной погрешности аналитической модели 81.27%. Во второй итерации значение тока принималось за 1 мкА, и в этом случае значение A оказалось равным 3.5687 В, а усредненная погрешность составила 52.98%. Затем было выполнено еще несколько расчетных итераций, в результате чего было установлено, что в наибольшей степени истинному значению тока с учетом заданной степени точности соответствует значение Id = 170 нА, при этом значение критерия A составило 0.0816 В, а усредненная погрешность модели – 3.16%.

Если же необходимо определить значение тока при работе умножителя в области сильной инверсии, например, с точностью до десятых долей мкА при амплитуде входного напряжения Va = = 0.7 В (>VT0) при сохранении значений остальных параметров, то уточненное значение Id составляет 1.0 мкА, при значении A = 0.3512 и соответствующей погрешности аналитической модели в 2.44%. Значение технологического коэффициента K рассчитывалось по выражению [20]

Результаты уточнения значения тока при работе в области слабой (Va = 0.2 В) и сильной инверсии (Va = 0.7 В) представлены соответственно на рис. 2а и рис. 2б.

Рис. 2.

Результаты итерационного уточнения значения параметра Id (Vsim – результаты моделирования, Vcalc – результаты расчетов) при работе умножителя в режиме слабой (а) и сильной (б) инверсии.

Таким образом, при достижении необходимой степени точности соответствия и использовании действительных значений остальных параметров можно утверждать, что установленное значение искомого параметра соответствует действительности со степенью достоверности, определяемой заданной степенью точности итерационного процесса и точностью оценочных моделей.

4. РЕЗУЛЬТАТЫ РАЗРАБОТКИ ИНТЕГРАЛЬНОГО УМНОЖИТЕЛЯ НАПРЯЖЕНИЯ

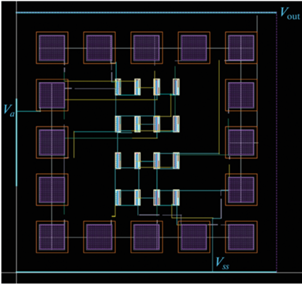

Разработка многокаскадного умножителя напряжения для беспроводных пассивных микроустройств выполнялась в САПР Virtuoso (Cadence) и Calibre Interactive (Mentor Graphics) по технологии КМОП 180 нм (TSMC). Моделирование разрабатываемого восьмикаскадного умножителя в программном модуле Virtuoso ADE (Spectre) на первых этапах разработки проводилось без учета влияния паразитных элементов. После построения топологии (рис. 3) и извлечения паразитных сопротивлений и емкостей посредством САПР Calibre Interactive было также проведено моделирование работы устройства с учетом влияния экстрагированных паразитных элементов (post-layout simulation). Площадь, занимаемая умножителем на кристалле, составила 0.029 мм2 (170 × 170 мкм).

Рис. 3.

Топология восьмикаскадного умножителя, построенная в Virtuoso Layout Suite по технологии КМОП 180 нм.

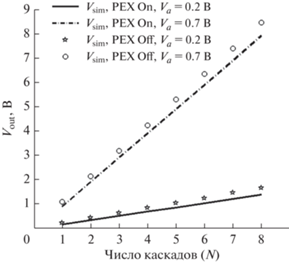

Сравнение результатов моделирования умножителя без учета и с учетом влияния извлеченных паразитных элементов для различных значений входных напряжений представлено на рис. 4. Из рисунка видно, что, во-первых, качественно результаты моделирования для обоих случаев соответствуют друг другу, что свидетельствует о корректности построения топологии согласно схеме умножителя. Во-вторых, заметно, что результаты моделирования умножителя без учета влияния паразитных элементов отклоняются от результатов моделирования с учетом их влияния в среднем на 17.9%. Такой характер зависимостей объясняется тем, что при схемном моделировании не учитывается вклад, вносимый паразитными сопротивлениями и емкостями при прохождении тока в умножителе во время процессов зарядки и разрядки конденсаторов.

Рис. 4.

Зависимость выходного напряжения от числа каскадов и входного напряжения при моделировании с учетом (PEX On) и без учета (PEX Off) экстрагированных паразитных элементов.

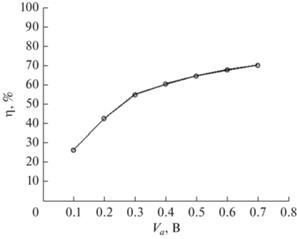

На рис. 5 показана зависимость эффективности умножения напряжения для разных амплитуд входного напряжения, полученная из результатов моделирования умножителя с учетом экстрагированных паразитных элементов и выражения для определения эффективности [3]

где Vout, sim – выходное напряжение умножителя, установленное из моделирования.Как видно из рисунка, при амплитуде входного напряжения ниже порогового напряжения (VT0 = 0.262 В) эффективность умножения напряжения существенно снижается, тогда как изменение эффективности в области сильной инверсии значительно слабее – при увеличении амплитуды в два раза эффективность увеличивается всего на 12%. Из выражения (7) и рис. 5 можно установить оценочное значение амплитуды входного напряжения, необходимое для работы системы, питаемой источником на основе разработанного умножителя. Поскольку напряжение питания для используемой технологии составляет 1.8 В, то с учетом предполагаемого снижения напряжения на стабилизаторе минимальное значение амплитуды составляет приблизительно 0.26 В.

ЗАКЛЮЧЕНИЕ

В статье представлена методика, применимая в случаях, когда значения параметров аналитических моделей микроэлектронных устройств неизвестны или известны с недостаточной степенью точности. Реализация методики основывается на использовании данных, полученных в результате измерения или высокоточного моделирования разрабатываемого устройства и принимаемых за образец для сравнения с результатами расчетов по аналитическим моделям. Таким образом, предлагаемая методика может служить для уточнения и определения параметров аналитических моделей электронных устройств, построенных на основе интегральных МОП-транзисторов, что позволяет значительно снизить погрешность этих моделей.

Также в работе представлены результаты разработки интегрального восьмикаскадного умножителя напряжения по технологии КМОП 180 нм для пассивных беспроводных устройств. Показано, что эффективность умножения напряжения в подпороговой области составляет от 25 до 50%, что позволяет получать выходное напряжение порядка 2.1 В при амплитудах входного напряжения от 260 мВ. Такого уровня выходного напряжения достаточно для формирования напряжения питания и обеспечения работы элементной базы технологии КМОП 180 нм.

Работа выполнена в рамках проекта “Разработка и исследование методов и средств мониторинга, диагностики и прогнозирования состояния инженерных объектов на основе искусственного интеллекта” (задание № FENW-2020-0022, номер работы в ЮФУ № ЛАБ0110/2020-01ДЦ).

При выполнении работы использовались программно-аппаратные средства ЦКП “Микросистемная техника и электронная компонентная база” МИЭТ.

Список литературы

Dabhi C.K. BSIM4 4.8.2 MOSFET Model / C.K. Dabhi, A. Dasgupta, H. Agrawal, N. Paydavosi, T.H. Morshed, D.D. Lu, W. Yang, M.V. Dunga, X. Xi, J. He, W. Liu, Kanyu, M. Cao, X. Jin, J.J. Ou, M. Chan // Berkeley, CA, University of California, 2020. 184 p.

Custom IC / Analog / RF Design / [Электронный ресурс]: https://www.cadence.com/en_US/home/tools/custom-ic-analog-rf-design.html // Cadence Design Systems, (дата обращения: 09.06.2022).

Sinyukin A.S., Konoplev B.G. Integrated CMOS Microwave Power Converter for Passive Wireless Devices // Russian Microelectronics. 2021. V. 50. № 3. P. 219–227.

Пат. 199930 Российская Федерация, МПК H02J 7/00 (2006.01), H02J 7/02 (2006.01), H02J 7/10 (2006.01). Умножитель напряжения для маломощных приложений / Б.Г. Коноплев, А.С. Синюкин; заявитель и патентообладатель ФГАОУ ВО “Южный федеральный университет” – № 2020117338; заявл. 26.05.20; опубл. 29.09.20, Бюл. № 28. 9 с.

Enz C.C. Charge-based MOS transistor modeling / C.C. Enz, E.A. Vittoz // Chichester, West Sussex, Wiley, 2006. 303 p.

Dickson J.F. On-Chip High-Voltage Generation in MNOS Integrated Circuits Using an Improved Multiplier Technique // IEEE Journal of Solid-state Circuits. 1976. V. SC-11. № 3. P. 374–378.

Taghadosi M., Albasha L., Quadir N.A., Rahama Y.A., Qaddoumi N. High Efficiency Energy Harvesters in 65nm CMOS Process for Autonomous IoT Sensor Applications // IEEE Access. 2018. V. 6. P. 2397–2409.

Zhang G., Wu D., Jia J., Gao W., Cai Q., Xiao W., Yu L., Tao S., Chu Q. Architecture Characteristics and Technical Trends of UHF RFID Temperature Sensor Chip // Active and Passive Electronic Components. 2018. V. 2018. Article ID 9343241. P. 1–8.

Sung G.-M., Chou H.-Y., Chen Z.-W. Radio Frequency Energy Harvesting IC for ISM-915 MHz and 2.45 GHz Wireless Transmitter // 2021 IEEE International Future Energy Electronics Conference (IFEEC), Taipei. 2021. P. 1–5.

De Souza C.P., Villarim A.W.R., Baiocchi O. A 20 mV Rectifier for Boosting Internet of Natural Things (IoNT) // 2018 IEEE 9th Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), Vancouver. 2018. P. 401–405.

Swangpattaraphon N. The Y.-K. Design Consideration of 433.92 MHz ISM Band RF Rectifier for Wireless IoT Cloud Application // 2019 IEEE 9th Annual Computing and Communication Workshop and Conference (CCWC), Las Vegas. 2019. P. 685–689.

Guler U., Jia Y., Ghovanloo M. A Reconfigurable Passive Voltage Multiplier for Wireless Mobile IoT Applications // IEEE Transactions on Circuits and Systems – II: Express Briefs. 2020. V. 67. № 4. P. 615–619.

Beriain A., Solar H., Duroc Y., Tedjini S. UHF RFID Voltage Multiplier design from a harmonic communication perspective // 2021 XXXIVth General Assembly and Scientific Symposium of the International Union of Radio Science (URSI GASS), Rome. 2021. P. 1–4.

Wagih M., Savanth A., Gamage S., Weddell A.S., Beeby S. CMOS UHF RFID Rectifier Design and Matching: an Analysis of Process and Temperature Variations // 2021 IEEE International Conference on RFID Technology and Applications (RFID-TA), Delhi. 2021. P. 271–274.

Chun A.C.C., Ramiah H., Mekhilef S. Wide Power Dynamic Range CMOS RF-DC Rectifier for RF Energy Harvesting System: A Review // IEEE Access. 2022. V. 10. P. 23948–23963.

Takacs A., Okba A., Aubert H., Charlot S., Calmon P.-F. Recent Advances in Electromagnetic Energy Harvesting and Wireless Power Transfer for IoT and SHM Applications // 2017 IEEE International Workshop of Electronics, Control, Measurement, Signals and their Application to Mechatronics (ECMSM), Donostia. 2017. P. 1–4.

Li P., Long Z., Yang Z. RF Energy Harvesting for Batteryless and Maintenance-Free Condition Monitoring of Railway Tracks // IEEE Internet of Things Journal. 2021. V. 8. № 5. P. 3512–3523.

Snyman J.A. Practical Mathematical Optimization: Basic Optimization Theory and Gradient-Based Algorithms / J.A. Snyman, D.N. Wilke // 2nd ed., Berlin: Springer, 2018, 372 p.

Reynders N. Ultra-Low-Voltage Design of Energy-Efficient Digital Circuits / N. Reynders, W. Dehaene // Cham, Springer, 2015, 192 p.

Baker R.J. CMOS: circuit design, layout, and simulation. Hoboken, NJ, Wiley, 2010. 1177 p.

Дополнительные материалы отсутствуют.

Инструменты

Микроэлектроника