Российские нанотехнологии, 2022, T. 17, № 1, стр. 29-45

ВОЗМОЖНОСТИ И ОГРАНИЧЕНИЯ КМОП-ТЕХНОЛОГИИ ДЛЯ ПРОИЗВОДСТВА РАЗЛИЧНЫХ МИКРОЭЛЕКТРОННЫХ СИСТЕМ И ПРИБОРОВ

В. А. Беспалов 1, Н. А. Дюжев 1, В. Ю. Киреев 1, *

1 Национальный исследовательский университет “МИЭТ”

Москва, Россия

* E-mail: valerikireev@mail.ru

Поступила в редакцию 01.12.2020

После доработки 01.12.2020

Принята к публикации 11.02.2021

Аннотация

Рассмотрены основные законы развития планарной КМОП-технологии (технологии, основанной на применении комплементарных полевых МОП-транзисторов, образованных слоями металла, оксида и полупроводника) за последние 50 лет. Показаны возможности и ограничения геометрического и эквивалентного масштабирования планарных и реберных полевых МОП-транзисторов. Приведены базовые нормы КМОП-технологии для различных приборов и на разных временных этапах ее развития. Проведено различие между технологической и проектно-топологической нормами в КМОП-технологии. Показаны экономические и технические ограничения закона Мура (Moore’s Law) для планарной КМОП-технологии и достижение технологического предела ее развития в течение текущего десятилетия. Доказано, что в ближайшие 30 лет магистральным направлением в развитии технологии устройств микроэлектроники будет направление, получившее название “Больше чем Мур” (More then Moore). Это направление связано с созданием многочисленных систем окружающего интеллекта, на основе процессов гетерогенной трехмерной (объемной) интеграции различных микросхем. При этом оптимальным вариантом являются расположение кристаллов микросхем в стеки (пачки) и их соединение вертикальными проводами, проходящими сквозь кремниевые кристаллы, и соединительными платами. Отметим, что при вертикальной сборке кристаллов в процессе гетерогенной интеграции большинство кристаллов с приборами и сквозными отверстиями будут иметь толщины менее 50 мкм, что потребует исследования механических свойств и прочности таких мембранных структур.

ОГЛАВЛЕНИЕ

Введение

1. Возможности и ограничения масштабирования планарной КМОП-технологии по технологической норме

2. Топологическая, проектная и проектно-топологическая нормы при проектировании интегральных микросхем

3. Экономические и технические ограничения закона Мура для планарной КМОП-технологии

Заключение

ВВЕДЕНИЕ

В основе любого производства интегральных микросхем (ИМС) (integral circuits – IC) или просто микросхем всегда лежит выбор базовой концепции, определяющей конструкцию микросхемы и технологию (базовый технологический процесс) ее изготовления. Начиная с 1970-х годов и по настоящее время базовой технологией производства ИМС является планарная КМОП-технология (planar complementary metal-oxide-semiconductor – planar CMOS-technology), основанная на использовании комплементарных МОП-транзисторов, разделенных областями изоляции (рис. 1) [1].

Рис. 1.

Поперечное сечение комплементарных (complementary) планарных (planar) КМОП-транзисторов, сформированных на объемной (bulk) кремниевой подложке с эпитаксиальным слоем: Lg – литографическая длина затвора; ${{L}_{{ph}}}$ – физическая длина затвора [1].

С появления планарной КМОП-технологии в начале 70-х годов XX века ее развитие в течение 50 лет базировалось на двух законах: экспериментальном экономическом законе Гордона Мура и техническом законе масштабирования (scaling), сначала геометрического (geometrical scaling) Роберта Деннарда (Dennard’s Scaling Theory), а затем эквивалентного масштабирования (equivalent scaling) [1–4].

В объединенном виде законы Мура и масштабирования постулируют: “Функциональные возможности запоминающих устройств, а именно: количество ячеек памяти и емкость памяти, и микропроцессоров, а именно: количество транзисторов, производительность и тактовая частота, должны каждые два года удваиваться на кристалле при постоянстве плотности мощности, обеспечивая при этом уменьшение стоимости изготовления одной функциональной единицы (ячейки памяти или транзистора) на 29% в год” [5–7].

Согласно [8] закон Мура основан на законе опыта (Experience Low) применительно к специфике микроэлектронного производства. Закон опыта открыт в конце 60-х годов прошлого века бостонской консалтинговой группой (Boston Consulting Group) в ходе эмпирических исследований изменения цен и издержек (затрат) в различных отраслях промышленности. Современная формулировка закона опыта: “При удвоении совокупного (накопленного, кумулятивного) объема произведенной продукции реальные (т.е. без учета инфляционной составляющей) затраты на производство единицы продукции уменьшаются на относительно постоянную величину ~10–30%” [9].

Таким образом, выполнение закона Мура путем удвоения КМОП-транзисторов на кристаллах микросхем каждые два года обеспечивает практически максимальную экономическую эффективность их производства в соответствии с законом опыта (29% из возможных 30%) [8].

Отметим, что закон Мура не является законом природы, а всего лишь эмпирическим и экономическим правилом, по которому происходит развитие американской компании Intel. Ее многолетнее лидерство в области разработки, технологии и производства ИМС и связанное с ним мощное мировое экономическое и научное влияние сделали закон Мура эталоном для развития и прогресса всей мировой микроэлектронной индустрии даже в случаях, когда выгоднее было снижать темпы развития [8].

1. ВОЗМОЖНОСТИ И ОГРАНИЧЕНИЯ МАСШТАБИРОВАНИЯ ПЛАНАРНОЙ КМОП-ТЕХНОЛОГИИ ПО ТЕХНОЛОГИЧЕСКОЙ НОРМЕ

Геометрическое масштабирование направлено на постоянное сокращение горизонтальных и вертикальных размеров элементов КМОП-транзисторов и связанное с ним улучшение их электрических параметров для повышения плотности упаковки и функциональных характеристик (скорость, мощность и надежность) логических приборов и устройств памяти. Масштабирование геометрических размеров элементов проводится после выбора одного из электрических параметров постоянным, обычно напряженности электрического поля или напряжения питания [5–7].

Эквивалентное масштабирование обеспечивает улучшение рабочих характеристик приборов и микросхем, изготовленных по КМОП-технологии, не за счет изменения характерных геометрических параметров КПОП-транзисторов, а путем использования новых материалов, новых операций и новых интегральных структур. Эквивалентное масштабирование может применяться как без геометрического масштабирования, так и совместно с ним, дополняя друг друга [4].

Однако, как любой экспоненциальный закон развития на ограниченных ресурсах, закон Мура не может выполняться в течение длительного времени, так как постоянно достигаются те или иные пределы. Об этом предупреждал сам автор закона [10]. Лишь эволюция конструкции полевых транзисторов (рис. 2) и совершенствование технологических операций их изготовления позволяли продлить действие закона Мура еще на несколько поколений [2, 5, 6].

Рис. 2.

Эволюция конструкции полевых транзисторов в процессе масштабирования КМОП-технологии: 1 – классический планарный полевой транзистор на объемной (bulk) кремниевой подложке (подробная структура показана на рис. 1); 2 – планарный полевой транзистор на подложке “кремний на изоляторе” (КНИ) (silicon on insulator – SOI) с частично обедненным слоем рабочего кремния (partially depleted SOI – PD-SOI); 3 – планарный полевой транзистор на подложке КНИ (SOI) с полностью обедненным ультратонким слоем рабочего кремния (fully depleted SOI – FD-SOI); 4 – реберный полевой транзистор (fin field effect transistor – Fin FET) на объемной (bulk) кремниевой подложке; 5 – реберный полевой транзистор (fin field effect transistor – Fin FET) на подложке КНИ (SOI) [2, 5, 6].

Микроэлектроника, базирующаяся на планарной КМОП-технологии, подошла к пределу своих возможностей по масштабированию (уменьшению линейных размеров) используемых полевых транзисторов (field effect transistors – FETs), как планарных (Planar FETs), так и реберных (Fin FETs) (рис. 2). А также достигла пределов по производительности, потребляемой мощности, а главное, по себестоимости передовых ИМС на их основе [1, 2, 6].

Как видно из зависимости на рис. 3, мировое микроэлектронное производство освоило уровень технологии (УТ) (Technology Node – Node – N) 3 нм [2, 3, 11] и вплотную подходит к физическим пределам, за которыми закон Мура перестанет действовать из-за атомарных ограничений структур полевых транзисторов и влияния скорости света на скорость передачи информации [12].

Рис. 3.

Достижения планарной КМОП-технологии за 2013–2021 гг. (точки) и прогноз (линия) масштабирования на 2022–2023 гг., полученные по наборам данных Института электротехники и электроники [2], Международной ассоциации производителей полупроводниковых приборов [3] и работы [11]. Уровень технологии эквивалентен термину Technology Node или размеру технологической нормы.

Технологическая норма при геометрическом масштабировании – это минимальное расстояние между параллельными линиями одинаковой ширины L в регулярной структуре с шагом ($pitch = P$ = L + S) и промежутком S = L = = $half~pitch$ = h – p, которое еще можно реализовать на функциональных слоях ИМС с помощью литографического оборудования в используемой технологии (рис. 4) [2, 7].

При таком определении технологическая норма совпадает с разрешением процессов литографии, т.е. минимальным размером элемента или зазора в регулярных структурах с минимальным шагом ($min~pitch$) [13]:

(1)

${{L}_{{{\text{min}}}}}\, = \,1{\text{/}}2min{\text{\;}}pitch\, = \,min{\text{\;}}half{\text{\;}}pitch\, = \,{\text{min\;}}(h - p).$В англоязычной литературе минимальный размер элемента часто называют критическим или характерным размером (critical dimension (CD) or feature size) [14].

Естественно, что минимальный размер элементов в регулярных структурах с промежутками больше ширины самих элементов или изолированных элементов, расстояние между которыми в 10 и более раз больше их характерных размеров, может быть значительно (в 1.3–1.8 раза) меньше за счет использования эффектов обужения ширины маскирующих покрытий (resist-pattern-thinning). К таким элементам относятся затворы комплементарных МОП-транзисторов в высокосовершенных микропроцессорах (МП) (microprocessor unit – MPU) [6, 13].

Технологическая норма выполняет в микроэлектронике еще одну важную функцию: по ней определяется уровень разрешения технологического процесса или сокращенно уровень технологии, используемый для производства ИМС. Например, если микросхема произведена по процессу с технологической нормой 350 нм, то в русскоязычной литературе этот процесс обычно обозначается как УТ 350 нм [1, 5, 6], а в англоязычной – как technological process resolution 350 nm или technological process with CD 350 nm [14, 15].

На примере КМОП-технологии микроэлектроники можно наглядно показать, что на разных этапах ее развития в качестве технологической нормы выступали минимальные размеры различных функциональных элементов и эффективные минимальные размеры, пересчитанные из площади формируемых различных ячеек микроэлектронных приборов [16].

С начала 1970-х до 2007 г. КМОП-технология использовала в основном геометрическое масштабирование с небольшими добавками эквивалентного, поэтому минимальный размер Lmin характеристического элемента, получаемый в процессах литографии, полностью определял УТ, т.е. технологическую норму.

С начала 1970-х до середины 1990-х годов наиболее быстро масштабировались динамические оперативные запоминающие устройства (ДОЗУ) (dynamic random access memory – DRAM), и минимальный размер элемента Lmin, соответствующий технологической норме, определялся по первому уровню разводки ДОЗУ (DRAM) [6, 14]:

С середины 1990-х до 2006 г. в микроэлектронном производстве происходило наибольшее масштабирование полевых транзисторов в МП, и в качестве технологической нормы использовалась литографическая длина затвора полевого МОП-транзистора Lg (рис. 1) [16]:

Первое пятилетие XXI века было отмечено ускоренным развитием высокосовершенных логических интегральных схем специального назначения (заказных) (Application Specific Integrated Circuit – ASIC) и электрически перепрограммируемой флеш-памяти (Flash memory) типа NAND (не “и”) (от англ. not and) с высокорегулярной структурой. Поэтому в международных прогнозах (The International Technology Roadmap for Semiconductors – ITRS) с 2006 г. заменили общие технологические нормы для DRAM (формула (2)) и MPU (формула (3)) отдельными технологическими нормами для Flash, DRAM, MPU и ASIC [16]. Причем для флеш-памяти в формуле (2) должно стоять $Flash~half~pitch$ поликремневой разводки первого уровня словарной шины (word line – WL) [2]:

(4)

$\begin{gathered} {{L}_{{{\text{min}}}}} = ~Flash~Poly~Silicon~(1{\text{/}}2)pitch = \\ = \,~Flash~Poly{\text{\;}}(h - p). \\ \end{gathered} $В 2007 г. разработчикам компании Intel для МП, изготовленного по УТ 45 нм, удалось достичь физической длины затвора (physical gate length) ${{L}_{{ph}}}$ = 25 нм (рис. 1) [16]. После этого масштабирование длины затвора планарных полевых транзисторов остановилось из-за резкого роста паразитных эффектов (утечки тока), связанных с коротким каналом [17].

В 2009 г. для микропроцессоров (MPU), в том числе для заказных (ASIC), был разработан УТ 32 нм, в котором литографическая длина затвора транзисторов Lg была увеличена по сравнению с УТ 45 нм, тогда как другие параметры транзисторов были уменьшены. При этом в международных прогнозах ITRS технологическая норма для УТ 32 нм определялась по формуле (3), где в качестве полушага (1/2 pitch или half pitch) использовались линии разводки первого металла (M1), т.е. [2, 16]:

(5)

$\begin{gathered} {{L}_{{{\text{min}}}}} = {\text{MPU/ASIC}}~M1~(1{\text{/}}2)~pitch = \\ = {\text{MPU/ASIC}}~M1~(h - p). \\ \end{gathered} $В период с 2007 по 2011 г. профессор электротехники и информатики в Калифорнийском университете в Беркли Чэньминь Ху (Chenming Hu) изобрел, разработал конструкцию и в компании Intel изготовил первые образцы Fin FETs (4 и 5 на рис. 2) [18].

С введением Fin FETs в процесс производства микропроцессоров на УТ 22 нм плотность транзисторов продолжала увеличиваться, в то время как литографическая длина затвора оставалась более или менее постоянной. Это связано с конструкцией Fin FETs (4 и 5 на рис. 2), в которой эффективная длина канала Lef определяется по формуле [14]:

где ${{H}_{{Fin}}}$ и ${{W}_{{Fin}}}$ – соответственно высота и ширина ребра реберного транзистора.Таким образом, если при геометрическом масштабировании минимальный характеристический размер Lmin в качестве технологической нормы полностью определял УТ, то по мере возрастания роли эквивалентного масштабирования (кардинального изменения конструкции транзисторов с УТ 22 нм) он теряет эту функцию [4, 16, 17]. Поэтому была введена характеристическая мера масштабирования, называемая “технологическим узлом” или просто “узлом” (Technology Node – Node – N), которая отражает условный размер минимального элемента Lmin (технологическую норму), как он изменялся бы при полностью геометрическом масштабировании того или иного основного технологического узла микроэлектронного изделия [4, 17].

Например, топологи и маркетологи компании Intel стали вычислять технологическую норму на основании масштабирования (уменьшения) площади шеститранзисторной ячейки статической памяти – самого популярного строительного блока МП. Именно из таких ячеек обычно состоят кэш-память и регистровый файл, которые могут занимать полкристалла, поэтому схему и топологию шеститранзисторной ячейки всегда тщательно доводят до минимально возможного геометрического предела, так что это хорошая мера плотности упаковки [19].

Действительно, если для старого УТ литографическая длина канала полевых транзисторов была ${{L}_{g}}$ = 65 нм, а площадь шеститранзисторной ячейки статической памяти составляла ${{S}_{{SR}}} = X$ мкм2, то для нового УТ литографическая длина канала полевых транзисторов стала ${{L}_{g}}$ = 54 нм, а площадь шеститранзисторной ячейки статической памяти за счет масштабирования металлизации уменьшилась до ${{S}_{{SR}}} = X{\text{/}}5$ мкм2. Уменьшение площади шеститранзисторной ячейки статической памяти в 5 раз соответствует уменьшению линейных размеров в 2.236 раза, т.е. с 65 до 28 нм. Таким образом, для нового УТ технологическая норма ${{L}_{{{\text{min}}}}}$ = = 28 нм, а про длину канала новых полевых транзисторов ${{L}_{g}}$ = 54 нм можно особо не говорить [19].

Для УТ с использованием Fin FETs, у которых ключевые размеры уже не связаны с разрешением литографии, скорости масштабирования транзисторов и всех остальных элементов цифровых микросхем логики и памяти окончательно разошлись. Единственной адекватной цифрой осталась площадь ячейки памяти, на основе которой сейчас определяют и сообщают об УТ 10, 7 и 5 нм. Отсюда и пошли расхождения технологических норм от Intel с другими компаниями: 28 нм у всех, 32 нм у Intel; 20 нм у всех, 22 нм у Intel; 10 нм у всех, 14 нм у Intel. Как показало дальнейшее развитие микроэлектроники (рис. 5, табл. 1), расчеты технологических норм компании Intel в итоге оказались более правильными и адекватными, чем у конкурентов [19].

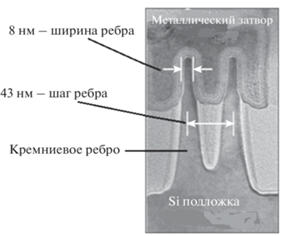

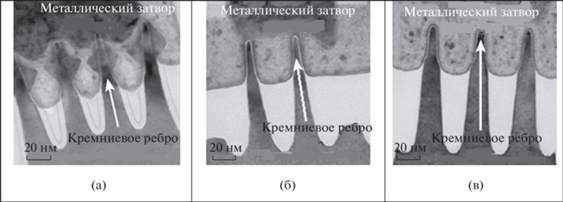

Рис. 5.

РЭМ-изображения логических микросхем на реберных полевых транзисторах (Fin FETs), производимых различными компаниями по различным уровням технологии: а – 14 нм (Intel (США)); б – 16 нм (TSMC (Тайвань)); в – 14 нм (Samsung (Корея)) [17].

Таблица 1.

Параметры логических микросхем на реберных полевых транзисторах (Fin FETs), производимых различными компаниями по различным уровням технологии (Technology Node)

| Параметры логической микросхемы на реберных полевых транзисторах (Fin FETs) | Компания производитель Intel (США) | Компания производитель TSMC (Тайвань) | Компания производитель Samsung (Корея) |

|---|---|---|---|

| Технологическая норма (Technology Node), нм | 14 | 16 | 14 |

| Длина затвора (Gate length), нм | 24 | 33 | 30 |

| Минимальный шаг контактов к затворам (Min contacted gate pitch), нм | 70 | 90 | 78 |

| Высота ребра под затвором (Fin height under gate), нм | 42 | 37 | 37 |

| Шаг ребер (Fin pitch), нм | 43 | 45 | 49 |

| Минимальный шаг металлической разводки (Min metal pitch), нм | 52 | 70 | 67 |

Как видно из табл. 1, топологическая длина канала Fin FETs, производимых по УТ (Technology Node) (14–16 нм), все еще больше, чем 20–25 нм, о которых говорилось выше. И это выглядит логичным фактом, так как физику прохождения носителей в канале полевых транзисторов не обманешь. Но из рис. 5a можно сделать и другой, более интересный вывод: если присмотреться, то становится понятно, что минимальный размер, имеющийся в реберных полевых транзисторах, – это не длина канала, а ширина ребра. Действительно, ширина ребра в микросхеме по техпроцессу Intel 14 нм составляет 8 (восемь!) нм (рис. 6) [19, 20].

Технологические нормы для разных типов ИМС через значения Lph, half pitch (h–p) и N приведены в табл. 2 [2, 21].

Таблица 2.

Технологические нормы микросхем логики, динамической и флэш-памяти высокого уровня и прогноз их развития (по состоянию на 2019 г.)

| Год начала производства | 2017 | 2019 | 2021 | 2023 | 2025 | 2027 | 2029 |

|---|---|---|---|---|---|---|---|

| Уровень технологии (УТ), нм Technology Node (N), nm |

7.0 | 5.0 | 3.0 | 2.5 | 1.8 | 1.2 | 0.8 |

| Логика: металл 1/2 шага, нм Logic: metal half pitch, nm |

14 | 12 | 10.5 | 7.5 | 7.0 | 7.0 | 7.0 |

| Физическая длина затвора Lph реберных полевых транзисторов, нм Physical gate length Lph Fin FETs, nm |

18 | 16 | 14 | 12 | 12 | 12 | 12 |

| Минимальная ширина ребра реберных полевых транзисторов, нм Minimal fin width Fin FETs, nm |

7.0 | 7.0 | 7.0 | 6.0 | 6.0 | 6.0 | 6.0 |

| Напряжение питания для логики Vdd, В Supply voltage for logic Vdd, V |

0.70 | 0.65 | 0.65 | 0.65 | 0.60 | 0.60 | 0.55 |

| Флэш (2D) памяти: Si-поли 1/2 шага, нм Flash (2D) memory: Si-poly half pitch, nm |

15 | 15 | 15 | 15 | 15 | 15 | 15 |

| Генерация флэш-памяти, Терабит/кристалл Generation flash-memory, Terabit/chip |

1 T | 1 T | 1.5 T | 2.5 T | 3.5 T | 4 T | 4 T+ |

| ДОЗУ: разводка 1/2 шага, нм DRAM: wiring half pitch, nm |

17.5 | 17 | 14.5 | 12 | 9 | 8 | 7.5 |

| Генерация ДОЗУ, Гигабит/кристалл Generation DRAM, Gigabit/chip |

8G | 16G | 16G | 32G | 32G | 32G | 32G+ |

2. ТОПОЛОГИЧЕСКАЯ, ПРОЕКТНАЯ И ПРОЕКТНО-ТОПОЛОГИЧЕСКАЯ НОРМЫ ПРИ ПРОЕКТИРОВАНИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ

С технологической нормой часто путают топологическую, проектную или проектно-топологическую норму. К сожалению, в учебной и технической литературе часто используются все три названия, хотя они относятся к единой норме, которую логически правильно называть проектно-топологической нормой (design and topological norm). Так как она неразрывно связана с процессом проектирования топологии ИМС (design of IC topology) в соответствии с правилами проектирования (IC design rules).

В состав правил проектирования включаются [6, 22]:

– номенклатура топологических элементов и/или их стандартных совокупностей (ячеек, блоков);

– требования к форме топологических элементов, ячеек, блоков;

– требования к максимальным и минимальным геометрическим размерам;

– требования к взаимному расположению топологических элементов, ячеек, блоков на кристалле, включая геометрические характеристики их взаимного расположения;

– электрические характеристики отдельных топологических элементов и их совокупностей (ячеек, блоков);

– процедурные требования к формированию топологического рисунка на кристалле.

Естественно, что технологическая норма значительно меньше проектно-топологической нормы, которая должна учитывать в качестве неизбежных допусков при получении размеров элементов микросхем множество факторов, связанных с неравномерностью по поверхности пластины толщины, глубины, высоты, ширины и формы профиля функциональных слоев, формируемых на операциях технологического процесса изготовления кристаллов ИМС.

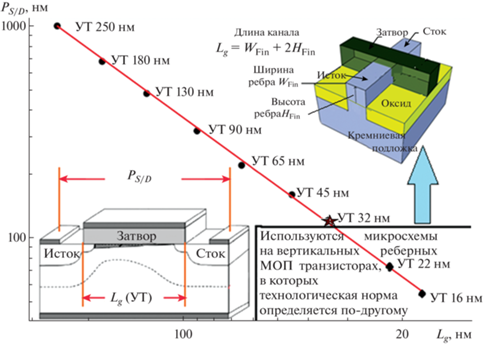

На рис. 7 приведена зависимость проектно-топологической нормы, определяемой по шагу ${{P}_{{S/D}}}$ между контактами к областям истока/стока (Source/Drain – S/D) планарных МОП-транзисторов (Metal Oxide Semiconductor Field Effect Transistors или Planar FETs), и технологической нормой, определяемой по литографической длине затвора (gate) Lg МОП-транзисторов [7]. Из приведенной зависимости видно, что проектно-топологическая норма практически в 4 раза больше технологической нормы, которая определяет для ИМС, изготавливаемых на планарных МОП-транзисторах, соответствующий диапазон уровней технологии (УТ 250 нм–УТ 45 нм).

Рис. 7.

Зависимость проектно-топологической нормы ${{P}_{{S/D}}}$ микросхем, изготовленных на планарных МОП-транзисторах, рассчитываемая по шагу между контактами к областям истока/стока, от технологической нормы Lg, фиксируемой по литографической длине затвора транзистора и определяющей УТ в диапазоне 250–45 нм [7].

Как отмечалось в разд. 2, для УТ 32 нм технологическая норма определяется по полушагу ($1{\text{/}}2~pitch$ или $half~pitch$) линии разводки первого металла (M1) (формула (5)), так как длина канала планарного транзистора Lg для этого УТ немного возрастает по сравнению с УТ 45 нм.

Для УТ, меньших 32 нм, при изготовлении микросхем используются вертикальные реберные МОП-транзисторы (FinFETs), для которых технологическая норма определяется по-другому и уже не соответствует литографической длине затвора.

Таким образом, проектно-топологические нормы, по которым проводится проектирование топологии ИМС, обычно в 2–4 раза больше, чем технологические нормы, из-за неравномерности используемых для воспроизведения разработанной топологии технологических процессов [7, 14, 19, 22].

3. ЭКОНОМИЧЕСКИЕ И ТЕХНИЧЕСКИЕ ОГРАНИЧЕНИЯ ЗАКОНА МУРА ДЛЯ ПЛАНАРНОЙ КМОП-ТЕХНОЛОГИИ

Закон Мура, еще не достигнув своих физических пределов, уже перестал выполнять свою экономическую функцию. В табл. 3 приведена стоимость изготовления одного полевого транзистора на кристаллах микросхем для разных уровней технологии (Technology Node) (размера технологической нормы) [23–25].

Таблица 3.

Стоимость изготовления полевых транзисторов на кристаллах микросхем для разных уровней технологии (размера технологической нормы)

| Год выпуска | 2004 | 2006 | 2008 | 2010 | 2012 | 2014 | 2016 | 2017 | 2018 | 2019 |

|---|---|---|---|---|---|---|---|---|---|---|

| Уровень технологии, нм | 130 | 90 | 65 | 40 | 28 | 20 | 16 | 10 | 7 | 7 ЭУФ |

| Стоимость изготовления одного полевого транзистора, ×10–8 $ | 5.29 | 4.01 | 2.82 | 1.94 | 1.40 | 1.42 | 1.62 | 1.53 | 1.55 | 1.46 |

Из данных таблицы видно, что после УТ 28 нм себестоимость полевых транзисторов перестает снижаться для УТ 20 нм и далее начинает возрастать относительно УТ 28 нм. Также в двух последних столбцах таблицы показано, что себестоимость транзисторов с УТ 7 нм, производимых с помощью процессов иммерсионной проекционной фотолитографии с длиной волны 193 нм при четверном экспонировании одного поля, выше, чем у их аналогов, реализованных с использованием процессов литографии на экстремальном ультрафиолете на длине волны 13.5 нм при однократном или двойном экспонировании одного поля [13].

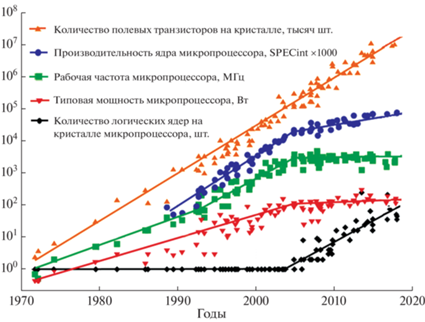

Как видно из зависимостей на рис. 8 [26–28], начиная с середины нулевых годов XXI века, несмотря на удвоение количества полевых транзисторов на кристалле одноядерных МП в соответствии с законом Мура, их производительность и рабочая частота практически перестали расти из-за ограничения уровня потребляемой электрической мощности, вследствие увеличения тепловыделения до предельного уровня [29].

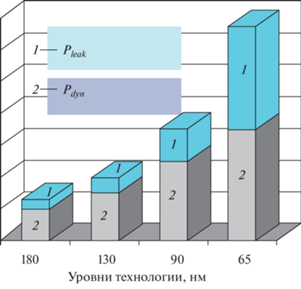

При классическом масштабировании Деннарда плотность мощности, выделяемая на единице площади кристалла, должна оставаться постоянной и не зависеть от размера элемента [7]. Однако при этом учитывается только динамическая мощность (dynamic power) ${{P}_{{dyn}}}$, потребляемая полевыми транзисторами во включенном (динамическом) состоянии (on), иногда называемая мощностью переключения (switching power). Тогда как с уменьшением размеров полевых транзисторов и напряжения питания резко возрастает потребление ими пассивной или статической мощности в выключенном (резервном, статическом) состоянии (off or standby) за счет увеличения токов утечки между электродами транзисторов. Эту статическую мощность обычно называют мощностью утечки (leakage power) ${{P}_{{leak}}}$ [6, 30].

До 2000 г. при уменьшении размера транзисторов в процессе масштабирования еще был резерв по энергопотреблению. Например, УТ уменьшился в 2 раза с 350 до 180 нм, количество транзисторов на кристалле выросло в 4 раза, а среднее энергопотребление каждого транзистора снизилось в 6–7 раз. Дело в том, что полевые МОП-транзисторы потребляют ток при переключении, а увеличение количества транзисторов шло преимущественно за счет роста кэш-памяти.

Кэш-память (cache memory) – это сверхбыстрая память, встроенная в процессор и применяемая им для временного хранения наиболее часто используемых данных. Полевые транзисторы кэш-памяти переключаются относительно редко, поэтому они потребляют значительно меньше динамической мощности, чем активные переключающиеся с тактовой частотой полевые транзисторы процессора. Эта разница и давала возможность поднимать тактовую частоту при том же тепловыделении.

При переходе с УТ 180 нм к УТ 130 нм в 2001 г. мощность утечки уменьшенных полевых транзисторов за счет роста токов утечки в выключенном состоянии израсходовала указанный резерв. С тех пор, несмотря на все ухищрения при масштабировании, резерва по мощности так и не смогли создать, а для энергосберегающих процессоров пришлось даже снижать тактовую частоту. По сути, в течение 2000-х годов незаметно произошла смена приоритетов при масштабировании, если раньше главным было уменьшение размеров полевых транзисторов, то сейчас – снижение токов и мощности утечки в них [31].

Зависимости динамической мощности ${{P}_{{dyn}}}$ и мощности утечки ${{P}_{{leak}}}$ полевых транзисторов микропроцессоров от УТ (технологической нормы) их производства приведены на рис. 9 и 10 [30, 32]. Из приведенных зависимостей видно, что при масштабировании, начиная с УТ 180 нм, наблюдается значительный рост мощности утечки полевых транзисторов МП, которая при УТ 65 нм составляет практически половину потребляемой МП мощности.

Рис. 9.

Зависимости динамической мощности ${{P}_{{dyn}}}$ и мощности утечки ${{P}_{{leak}}}$ полевых транзисторов микропроцессоров от уровня технологии (размера технологической нормы) их производства [32].

Рис. 10.

Зависимости динамической мощности ${{P}_{{dyn}}}$, мощности утечки ${{P}_{{leak}}}$ и доли мощности утечки от общей потребляемой мощности ${{P}_{{leak}}}{\text{/}}({{P}_{{dyn}}} + {{P}_{{leak}}})$ полевых транзисторов микропроцессоров от уровня технологии (размера технологической нормы) их производства [30].

А из зависимостей на рис. 8 следует, что до 2004 г. повышение производительности МП происходило за счет усложнения единственного вычислительного (логического) ядра и повышения рабочей частоты МП. С 2004 г. началась эра многоядерных МП, в которых повышение производительности осуществляется путем размещения на кристалле МП нескольких вычислительных (логических) ядер [29].

Первоначально Гордон Мур постулировал, что удвоение функциональных возможностей микросхем будет осуществляться за счет четырех движущих факторов [6]:

– увеличения диаметра кремниевых пластин;

– увеличения площади кристалла;

– уменьшения минимального размера (масштабирование);

– усовершенствования конструкции и топологии микросхемы.

Однако с 1960 г. до начала XXI века диаметр обрабатываемых кремниевых пластин увеличился с 13 мм (0.5 дюйма) до 300 мм (12 дюймов), и дальнейший переход на диаметр пластин 450 мм (18 дюймов), планируемый на 2016 г. [2, 3], задерживается уже до 2021 г. из-за необходимости дорогостоящей переделки технологического оборудования и прежде всего систем автоматической загрузки/выгрузки/перегрузки таких тяжелых пластин [5, 33].

Чем меньше площадь литографического поля, тем более высокое разрешение литографических систем можно получить. Поэтому в 2004 г. максимальный размер кристаллов микросхем был ограничен литографическим полем 26 × 33 мм и с тех пор сохраняется постоянным [13].

Уменьшение минимального размера элементов микросхем (масштабирование технологической нормы) увеличивает количество операций в технологических маршрутах. Это требует роста используемых в производстве номенклатуры и числа все более сложного и прецизионного, а значит, более дорогостоящего специального технологического оборудования (СТО). Соответственно, становится многочисленнее, сложнее и дороже оборудование инженерной инфраструктуры, обеспечивающее СТО энергоносителями и уровнем электронной гигиены, а также комплекты фотошаблонов и технологической оснастки.

Все это способствует резкому росту стоимости фабрик с повышением УТ (уменьшением технологической нормы) производимых ИМС. В [34] Гордон Мур обратил внимание на то, что “стоимость строительства новой более современной фабрики по производству микросхем удваивается примерно каждые 4 года”. Этот менее известный его прогноз получил название “второго закона Мура” (Moore’s Law 1995), который в дальнейшем был переформулирован как “стоимость новых полупроводниковых производств растет примерно на порядок за 20 лет”. В такой формулировке данную закономерность иногда также называют законом Рока (Rock’s Law) в честь Артура Рока, который в 1968 г. помог своими инвестициями основать корпорацию “Intel” (США) [35].

На рис. 11 приведена зависимость стоимости фабрик по производству микросхем от времени запуска и УТ [6, 14, 33, 35], из которой видно, что второй закон Мура или закон Рока хорошо соблюдается за последние 50 лет развития производства микросхем по КМОП-технологии. К стоимости фабрик по производству ИМС необходимо прибавить стоимость проектирования (разработки) кристалла микросхемы, а также затраты на изготовление комплекта фотошаблонов, их коррекцию и на процесс изготовления кристаллов ИМС с учетом выхода годных [6, 13].

На рис. 12 приведена зависимость стоимости проектирования кристалла микросхемы от УТ (размера технологической нормы) в течение временного периода 2007–2019 гг. [36]. Согласно этой зависимости средняя стоимость проектирования кристаллов ИМС по УТ 28 нм составляет 51.3 млн долл., по УТ 16 нм – 106.3 млн долл. и по УТ 5.0 нм – 542.2 млн долл. [36, 37].

Рис. 12.

Зависимость стоимости проектирования кристалла микросхемы от УТ (размера технологической нормы) в течение 2007–2019 гг.: 1 – аттестация интеллектуальной собственности, 2 – архитектура, 3 – верификация, 4 – проектирование на физическом уровне, 5 – программное обеспечение, 6 – создание опытных образцов, 7 – аттестация конструкции [36].

В табл. 4 приведены стоимости разработки и изготовления комплекта фотошаблонов и стоимости разработки технологических процессов для производства ИМС с различными УТ (различными технологическими нормами) [33]. Из данных таблицы видно, что:

Таблица 4.

Стоимость разработки и изготовления комплекта фотошаблонов и разработки технологических процессов для производства ИМС с различными уровнями технологии

| Уровень технологии, нм | 250 | 180 | 130 | 90 | 65 | 45 | 32 |

| Стоимость разработки и изготовления комплекта фотошаблонов, млн $ | 0.25 | 0.42 | 0.75 | 1.20 | 1.85 | 2.75 | 3.50 |

| Стоимость разработки технологических процессов, млн $ | 102 | 150 | 210 | 310 | 402 | 600 | 900 |

– стоимости разработки и изготовления комплекта фотошаблонов для микросхем с УТ 45 нм в 11 раз больше, чем для микросхем с УТ 250 нм и составляет 2750 тыс. долл.;

– стоимость разработки технологических процессов производства микросхем с УТ 32 нм в 6 раз больше стоимости разработки технологических процессов для микросхем с УТ 180 нм и достигает 900 млн долл.

Стоимость научно-исследовательских и опытно-конструкторских работ в области технологии кристаллов микросхем с УТ 45 нм составила 2.4 млрд долл., а кристаллов микросхем с УТ 32 нм – 3.0 млрд долл. [38].

Суммируя все затраты, можно констатировать, что для открытия полного производственного цикла по КМОП-технологиям с УТ в диапазоне 28–22 нм требуется ~50 млрд долл., с УТ в диапазоне 16–10 нм – ~80–90 млрд долл., а с УТ в диапазоне 7.0–5.0 нм – ~110–120 млрд долл. [39, 40]. Чтобы окупить такие гигантские затраты, надо обеспечить продажу огромного количества произведенных кристаллов микросхем, т.е. фактически монополизировать весь мировой микроэлектронный рынок. Естественно, на такое способны только самые большие, богатые и передовые компании и кремниевые фабрики, производящие микросхемы.

Напомним, что среди производителей микросхем можно выделить две большие группы [6]:

– традиционные вертикально интегрированные полупроводниковые компании (Integrated Device Manufacturer – IDM), ведущие самостоятельно разработку, проектирование, производство и маркетинг микросхем;

– и тандемы (fabless – foundry): фирм разработчиков без собственных производственных мощностей (fabless) и кремниевых фабрик (foundries).

Если следовать направлению развития микроэлектроники, определяемому законом Мура, которое получило название “Больше Мура” (More Moore) [2, 4, 5], то по мере удорожания производства микросхем с уменьшением минимального размера элементов (технологической нормы) происходят естественные процессы уменьшения количества IDM-компаний и кремниевых фабрик (foundries), которые могут выдержать экономическую и технологическую конкуренцию.

В табл. 5 показана динамика уменьшения количества компаний и кремниевых фабрик по мере повышения УТ (снижения размера технологической нормы) [41–43]. Из данных таблицы видно, что субдесятинанометровые технологии в соответствии с законом Мура способны развивать в мире только две IDM-компании: Samsung (Корея) и Intel (США) и одна кремниевая фабрика TSMC (Taiwan Semiconductor Manufacturing Company) (Тайвань).

Таблица 5.

Динамика изменения количества компаний и кремниевых фабрик (1-я строка) по мере повышения уровня технологии (уменьшения размера технологической нормы) (3-я строка)

| 30 | 28 | 21 | 15 | 14 | 10 | 6 | 4 | 3 | 3 | 3 |

|---|---|---|---|---|---|---|---|---|---|---|

| ПАО “Микрон” | ||||||||||

| (Россия) | АО | |||||||||

| SilTerra | “Ангстрем-Т”▲ | |||||||||

| X-FAB | (Россия) | |||||||||

| Dongbu HiTek | ПАО “Микрон” | |||||||||

| ADI | ADI | |||||||||

| Atmel | Atmel | |||||||||

| Rohm | Rohm | |||||||||

| Sanyo | Sanyo | АО | ||||||||

| Mitsubishi | Mitsubishi | “Ангстрем-Т”▲ | ||||||||

| Hitachi | Hitachi | ПАО “Микрон” | ||||||||

| Cypress | Cypress | Cypress | ||||||||

| Sony | Sony | Sony | ||||||||

| Infineon | Infineon | Infineon | ||||||||

| Sharp | Sharp | Sharp | ||||||||

| Freescale | Freescale | Freescale | ПАО “Микрон”* | |||||||

| Renesas (NEC) | Renesas | Renesas | Renesas | Renesas | ||||||

| Toshiba | Toshiba | Toshiba | Toshiba | Toshiba | ||||||

| Fujitsu | Fujitsu | Fujitsu | Fujitsu | Fujitsu | ||||||

| TI | TI | TI | TI | TI | ||||||

| Panasonic | Panasonic | Panasonic | Panasonic | Panasonic | Panasonic | |||||

| STMicroelectronics | STM | STM | STM | STM | STM | |||||

| HLMC | HLMC | HLMC | HLMC | HLMC | HLMC | |||||

| UMC | UMC | UMC | UMC | UMC | UMC | |||||

| IBM | IBM | IBM | IBM | IBM | IBM | IBM | ||||

| SMIC | SMIC | SMIC | SMIC | SMIC | SMIC | STM | ||||

| AMD | AMD | AMD | GlobalFoundries | GF | GF | GF | GF | |||

| Samsung | Samsung | Samsung | Samsung | Samsung | Samsung | Samsung | Samsung | Samsung | Samsung | Samsung |

| TSMC | TSMC | TSMC | TSMC | TSMC | TSMC | TSMC | TSMC | TSMC | TSMC | TSMC |

| Intel | Intel | Intel | Intel | Intel | Intel | Intel | Intel | Intel | Intel | Intel |

| TL | TL | TL | TL | TL | TL | TL | TL | TL | TL | TL |

| 180 нм | 130 нм | 90 нм | 65 нм | 45/40 нм | 32/28 нм | 22/20 нм | 16/14 нм | 10 нм | 7 нм | 5 нм |

Примечание. Приведены компании и кремниевые фабрики, обеспечивающие массовое производство микросхем на базе высокопроизводительных процессов оптической нанолитографии с использованием УФ, включая экстремальное УФ с длиной волны 13.5 нм. Компании, которые могут реализовать приведенные в таблице размеры с помощью процессов электронной литографии и наноимпринтлитографии, не рассматриваются из-за низкой производительности указанных процессов литографии [13]. TSMC – Taiwan Semiconductor Manufacturing Company (Тайвань); AMD – Advanced Micro Devices (США); SMIC – Semiconductor Manufacturing International Corporation (Китай); IBM – International Business Machines (США); UMC – United Microelectronics Corporation (Тайвань); HLMC – Shanghai Huali Microelectronics Corporation (Китай); STM – STMicroelectronics (Франция); GF – GlobalFoundries (Сингапур); TI – Texas Instruments (США); ADI – Analog Devices Inc. (США); компании Panasonic, Fujitsu, Toshiba, Renesas, Sharp, Sony, Hitachi, Mitsubishi, Sanyo, Rohm (Япония); компании Intel, Freescale Semiconductor, Cypress Semiconductor, ON Semiconductor, Atmel (США); компании Infineon Technologies, X-FaB (Германия); компании Samsung, Dongbu HiTek (Корея); SilTerra (Малайзия).

* Процессы находятся в стадии разработки [42].

▲ С 28 октября 2019 г. компания находится в состоянии банкротства [43].

Согласно международному прогнозу [2] и рис. 3 микроэлектроника, базирующаяся на планарной КМОП-технологии, в соответствии с законом Мура подходит к своему физическому пределу. Действительно, в 2021 г. реально освоен УТ 3.0 нм, а к 2023–2024 гг. будет достигнут и последний УТ 1.0–0.8 нм.

Приведенный в табл. 2 прогноз достижения различных промежуточных УТ (3.5, 2.5, 1.8 и 1.2 нм) и последнего предельного УТ 0.8 нм к 2029 г. отражает экономическую эффективность следования закону Мура, а не технические возможности технологии микроэлектроники.

Действительно, для реализации указанных технологий уже изготовлены и испытаны:

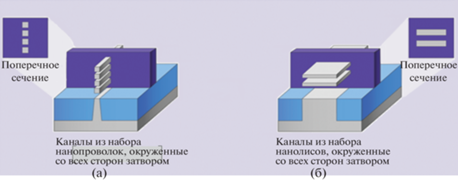

– два варианта конструкций полевых транзисторов с затвором, окружающим наборы каналов различной формы со всех сторон (Gate-All-Around FET – GAA FET), показанные на рис. 13 [44–46] и образующие в наносхемах систему (front-end-of-line – FEOL);

– основные узлы системы металлизации (back-end-of-line – BEOL) и узлы системы (middle-of-line – MOL), соединяющей системы FEOL и BEOL [47].

ЗАКЛЮЧЕНИЕ

Начинающееся десятилетие будет последним периодом развития микроэлектроники по закону Мура, т.е. по направлению, которое получило название “Больше Мура” (More Moore). Участвовать в этом развитии из-за его дороговизны и сложности смогут только три ведущие мировые компании по производству интегральных микросхем и систем на их основе: TSMC (Тайвань), Intel (США) и Samsung (Корея).

Для остальных участников микроэлектронного консорциума в дорожных картах [2, 4, 5] выделяются два направления: “За пределами КМОП” или “Вне КМОП” (Beyond CMOS) и “Больше чем Мур” (More then Moore).

Направление “За пределами КМОП” относится к фундаментальному научно-технологическому направлению развития микроэлектроники, основанному на принципе функционального масштабирования (functional scaling) [4, 5, 48]. Этот принцип заключается в том, что микросхему (систему, прибор) с определенными функциональными (рабочими) характеристиками, изготовленную с помощью КМОП-технологии, пытаются реализовать с помощью альтернативных инновационных технологий. Причем реализация должна быть такой, чтобы функции новой микросхемы были идентичны функциям оригинальной микросхемы и по крайней мере одна из ее рабочих характеристик улучшалась, а остальные – не ухудшались [4].

Инновационные технологии, к которым относится большинство нанотехнологий, могут быть реализованы с различной архитектурой (аналоговой, квантовой, морфологической) и разными видами представления данных (аналоговыми, квантовыми, топологическими). При этом открываются возможности применения материалов, отличных от кремния, например соединений углерода и A3B5, германия, магнитных и наноструктурированных пленок, а также создания систем на одноэлектронных транзисторах (single electron transistor – SET), на спинтронных, квантовых, молекулярных и ферромагнитных эффектах. На практике функциональное масштабирование предполагает такое проектирование микросхемы, при котором ее последующее изготовление возможно по различным технологическим нормам [48].

Естественно, что на направление “За пределами КМОП”, в первую очередь, переориентируются компании, фирмы-разработчики, кремниевые фабрики, производственные участки и линейки без значительных заделов в области разработки и изготовления микросхем по КПОП-технологии.

Направление “Больше чем Мур” является магистральным направлением дальнейшего развития технологии и производства микроэлектроники, в основе которого лежат процессы гетерогенной 3D-интеграции различных микросхем логики и памяти, наборов микро- и наносенсоров, микро- и наноэлектромеханических систем (МЭМС и НЭМС) и других цифровых и аналоговых информационно-коммуникационных устройств, реализующих всеобъемлющую область применения под названием “окружающий интеллект” (Ambient Intelligence – AmI) [5].

Окружающий интеллект неразрывно связан с “искусственным интеллектом” (ИИ) (Artificial Intelligence – AI), можно сказать, что окружающий интеллект это, по сути, ИИ в окружающей среде. С другой стороны, ИИ обязан своим успехом феноменальному развитию информационных и коммуникационных технологий, основанных на законах и достижениях КМОП-технологии микроэлектронного производства [49].

Современное определение окружающего интеллекта дано в [50]: “Окружающий интеллект – это междисциплинарный подход, направленный на улучшение взаимодействия среды и людей друг с другом. Конечная цель подхода – сделать места, в которых люди живут и работают, более удобными, выгодными и благоприятными для них. “Умные дома” являются одним из примеров таких систем, но эту идею можно распространить на все области жизни людей: на учебные заведения, объекты здравоохранения и отдыха, рабочие места на фабриках, заводах и в офисах, общественный и личный транспорт, охрану окружающей среды и безопасность и на другие среды, включая целые города”.

В мире интеллектуального окружения устройства работают сообща, чтобы поддерживать людей в выполнении их повседневных действий, задач и ритуалов простым, естественным образом, используя информацию и интеллект, который скрыт в сети, соединяющей эти устройства. В качестве такой коммуникационной сети будет использован Интернет, который действительно превратился в беспроволочный, вездесущий и постоянно расширяющийся всемирный коммуникатор, уже называемый “Интернетом Всего” (Internet of Everything – IoE) [51].

Таким образом, по прогнозам и дорожным картам системы окружающего интеллекта и входящие в их состав подсистемы ИИ, IoE, а также доверенные (защищенные) интеллектуальные сенсорные подсистемы ближайшие 30 лет будут основными двигателями (drivers) развития микроэлектроники, последовательно заменив настольные компьютеры, планшеты и смартфоны [2, 48–51]. Технологическое обеспечение этого развития будет связано с разработкой и изготовлением систем и микросхем ИИ и нейросетей с подключенными к ним наборами датчиков, имитирующих человеческие чувства: зрение, слух, обоняние, вкус и осязание. Специалисты оценивают, что количество подключенных к сети датчиков к 2020 г. превысит 50 млрд [52].

Несомненно, что технологическое развитие всех компаний, кремниевых фабрик и фирм-разработчиков, имеющих значительные заделы по разработке и производству микросхем, но не выдержавших конкурентную борьбу с Samsung, Intel и TSMC, будет связано с магистральным направлением “Больше чем Мур” [2, 4, 5]. При этом оптимальным вариантом гетерогенной 3D-интеграции являются расположение кристаллов микросхем в стеки (пачки) (stacks) и их соединение вертикальными проводами, проходящими сквозь кремниевые кристаллы, и интерфейсными платами – интерпозерами (interposers). Отметим, что при такой вертикальной сборке кристаллов в процессе гетерогенной интеграции большинство кристаллов с приборами и сквозными отверстиями будут иметь толщины менее 50 мкм, что потребует исследования механических свойств и прочности таких фактически мембранных структур.

Работа выполнена с использованием оборудования ЦКП “МСТ и ЭКБ” (МИЭТ) при финансовой поддержке Министерства науки и высшего образования Российской Федерации (№ 075-03-2020-216, 0719-2020-0017, мнемокод FSMR-2020-0017).

ДОПОЛНИТЕЛЬНАЯ ИНФОРМАЦИЯ

Более подробное описание развития и конструкции отдельных узлов микросхем с технологическими нормами (УТ) в диапазоне 1.0–5.0 нм приведено в пленарном докладе академика РАН, генерального директора АО НИИ молекулярной электроники (АО “НИИМЭ”) Г.Я. Красникова “Возможности микроэлектронных технологий с топологическими размерами менее 5 нм” на VI Международном форуме “Микроэлектроника 2020”, Республика Крым, Ялта, 27.09–03.10.2020 г. Видеозапись размещена на сайте АО “НИИМЭ” – https://www.niime.ru/press-center/news/.

Развернутое описание конструкции приборов и физики их работы по направлению “Вне КМОП” приведено в пленарном докладе академика РАН, заведующего кафедрой квантовой физики и наноэлектроники Национального исследовательского университета “МИЭТ”, главного научного сотрудника Физического института РАН А.А. Горбацевича “Квантовые решения для снижения энергопотребления логических схем” на VI Международном форуме “Микроэлектроника 2020”, Республика Крым, Ялта, 27.09–03.10.2020 г. Краткое перечисление возможностей квантовых технологий в микроэлектронике из доклада А.А. Горбацевича приведено на сайте https://news.myseldon.com/ru/news/index/235797861.

Указанные доклады, как и все доклады VI Международного форума “Микроэлектроника 2020”, опубликованы в специальном выпуске журнала “Наноиндустрия” за 2021 г.

Список литературы

Дюжев Н.А., Киреев В.Ю. Элементный базис нано- и микросистемной техники. Учебное пособие. М.: ИПК МИЭТ, 2019. 139 с.

International Roadmap for Devices and SystemsTM (IRDS). 2018 Edition. Executive Summary. The Institute of Electrical and Electronics Engineers, Incorporated, 2019. 32 p.

The International Technology Roadmap for Semiconductors. 2013 Edition. Executive Summary. San Jose. CA: Semiconductor Industry Association, 2013. 10 p.

Вернер В., Кузнецов Г., Сауров А. // Наноиндустрия. 2015. № 4 (58). С. 22.

Свистова Т.В. Основы микроэлектроники: учебное пособие. Воронеж: Воронеж. гос. тех. ун-т, 2017. 148 с.

Киреев В.Ю. Введение в технологии микроэлектроники и нанотехнологии. М.: Изд-во “ЦНИИХМ”, 2008. 427 с.

Цветков Ю.Б. Процессы и оборудование микротехнологии. Часть 1. М.: Изд-во МГТУ им. Н.Э. Баумана, 2017. 168 с.

Киреев В. // Электроника: НТБ. 2007. № 1. С. 4.

Уорд К. Стратегический управленческий учет. Перевод с англ. М.: Изд-во “Олимп-Бизнес”, 2002. 435 с.

Moore G.E. // Solid-State Circuits Conference. IEEE International Digest of Technical Papers. 2003. V. 1. P. 20. https://doi.org/10.1109/ISSCC.2003.1234194

WikiChip. 5 nm lithography process. https://en.wikichip.org/wiki/5_nm_lithography_process

PCNews. 12.07.2008. 10 лет до 10 нм: закон Мура все еще работает. https://pcnews.ru/news/10-channalweb-intel-pat-gelsinger-100-tsmc-45-2009-1965-33-1971-1978-1989-1997-25-2005-65-pentium-233904.html

Киреев В.Ю. Нанотехнологии в микроэлектронике. Нанолитография – процессы и оборудование. Долгопрудный: Издательский Дом “Интеллект”, 2016. 320 с.

Handbook of Semiconductor Manufacturing Technology / Eds. Nishi Y., Doering R. New York: Marcell Dekker Inc., 2008. 1722 p.

Semiconductor device fabrication. https://en.wikipedia.org/wiki/Semiconductor_device_fabrication

WikiChip. Technology Node. https://en.wikichip.org/wiki/technology_node

Евгений @ Tiberius. Технологии микроэлектроники на пальцах: “закона Мура”, маркетинговые ходы и почему нанометры нынче не те. https://aftershock.news/?q=node/745507

Perry T.S. // Spectrum IEEE. 2020. № 5. P. 47.

Валерий Шунков. Проектные нормы в микроэлектронике: где на самом деле 7 нанометров в технологии 7 нм? 24.09.2018 г. https://habr.com/ru/post/423575/

WikiChip. 14 nm lithography process. https://en.wikichip.org/wiki/14_nm_lithography_process

Moore S.K. // Spectrum IEEE. 2020. № 8. P. 24.

Ланцов В.Н. Проектирование заказных интегральных схем на КМОП. Учебное пособие. Владимир: Изд-во Владимир. гос. ун-та, 2009. 224 с.

Fritze M., Cheetham P., Lato J., Syers P. // STEPS: Science. Technology. Engineering and Policy Studies. 2016. № 3. P. 35.

Макушин М. // Электроника: НТБ. 2014. № 3. С. 134.

Темпы-освоения новых топологических норм замедляются. https://russianelectronics.ru/tempy-osvoeniya-novyh-topologicheskih-norm-zamedlyayutsya

The new global ecosystem in advanced computing: Implications of U.S. competitiveness and national security. Washington DC: The National Academic Press, 2012. 116 p.

Rupp K. 42 years of microprocessor trend data. karlrupp.net/2018/02/42. years-of-microprocessor-trend-data/

Rupp K. 48 years of microprocessor trend data. July 16, 2020. github.com/karlrupp/microprocessor-trend-data

Chevalier G. Some reasons why deep learning a bright future. Dec. 29, 2019. https://www.neuraxio.com/en/blog/deep-learning/2019/12/29/why-deep-learning-has-a-bright-future.html

Narendra S. // Journal on Emerging Technologies in Computing Systems. 2005. V. 1. № 1. P. 7.

Евгений Tiberius. Технологии микроэлектроники на пальцах: “закона Мура”, маркетинговые ходы и почему нанометры нынче не те. Часть 2. https://aftershock.news/?q=node/746092

Power consumption: components of power consumption. https://semiengineering.com/knowledge_centers/low-power/low-power-design/power-consumption/

Бондарь Д. // Электронные компоненты. 2015. № 3. С. 12.

Moore G. // Proc. SPIE. 1995. V. 2437. P. 2. https://doi.org/10.1109/N-SSC.2006.4785861

Аноприенко А.Я. // Вестник Донецкого национального технического университета. 2016. Т. 2. № 2. С. 3.

Перспективные технологии для процессов с проектными нормами 22 нм и менее. Зарубежная электронная техника. Вып. 25 (6674) от 20.12.2018. С. 17.

LaPedus M. // Semiconductor Engineering, November 19, 2018. https://semiengineering.com/foundries-prepare-for-battle-at‑22nm/

Юдинцев В. // Электроника: НТБ. 2008. № 3. С. 124.

Хэйер Й., Пятенко А. // Электроника: НТБ. 2010. № 6. С. 126.

Экономические аспекты освоения топологий 28 нм и менее. Зарубежная электронная техника. Вып. 30 от 13.10.2016. С. 4.

Technology Node. https://en.wikichip.org/wiki/technology_node

Технологии ПАО “Микрон”. https://www.mikron.ru/capabilities/technology/

История компании АО “Ангстрем-Т” 2007–2020 гг. https://www.tadviser.ru/index.php/%D0%9A%D0%BE%D0%BC%D0%BF%D0%B0%D0%BD%D0%B8%D1%8F:%D0%90%D0%BD%D0%B3%D1%81%D1%82%D1%80%D0%B5%D0%BC-%D0%A2

Gate-All-Around FET (GAA FET). https://semiengineering.com/knowledge_centers/integrated-circuit/transistors/3d/gate-all-around-fet/

Валерий Шунков. Почему кремний и почему КМОП? https://habr.com/ru/post/448320/

Peide Y.E., Ernst T., Khare M.V. // Spectrum IEEE. 2019. № 8. P. 30.

Horiguchi N., Tokei Z. A View on the Logic Technology Roadmap. https://www.semiconductor-digest.com/2020/11/23/a-view-on-the-logic-technology-roadmap/

The International Technology Roadmap for Semiconductors 2.0. 2015 Edition. Beyond CMOS. San Jose. CA: Semiconductor Industry Association et al. 2015. 87 p.

Gams M., Gu I.Y-H., Munoz A., Tam V. // J. Ambient Intell. Smart Environ. 2019. № 11. P. 71.

Augusto J.C., McCullagh P. // Computer Science and Information Systems, 2007. V. 4. № 1. P. 1. https://doi.org/10.2298/CSIS0701001A

Сергей Яроцкий. Искусственный интеллект, разработка и области применения. 06.05.2019. https://sci-news.ru/2019/oblasti-primenenija-trendy-i-tehnologii-iskusstvennogo-intellekta/

Перспективные системы искусственного интеллекта требуют большей мощности. 14 сентября 2018. https://www.compel.ru/lib/94727

Дополнительные материалы отсутствуют.

Инструменты

Российские нанотехнологии